碳化硅賦能浪潮教程:替代Si 和SiC MOSFET的方案

碳化硅(SiC)憑借其優異的材料特性,在服務器、工業電源等關鍵領域掀起技術變革浪潮。本教程聚焦 SiC 尤其是 SiC JFET 系列器件,從碳化硅如何重構電源設計邏輯出發,剖析其在工業與服務器電源場景的應用價值。

我們已經介紹了 碳化硅如何革新電源設計、工業與服務器電源。

本文為第二篇,將介紹三種替代 Si 和 SiC MOSFET的方案

SiC JFET、SiC Combo JFET、SiC Cascode JFET、SiC MOSFET的核心要點SiC JFET

● 常開型

● 極低的導通電阻 RDS(on)

● 柵極偏置電壓為 0V 時導通

● 柵極驅動電壓范圍:-20V至+2V

● 通過柵極電阻RG 控制開關速度

● 可利用 PN 結二極管作為芯片溫度TJ 傳感器實現自監測

SiC Combo JFET

● 常閉型

● 可獨立訪問 MOSFET 與 JFET 柵極

● 集成芯片溫度檢測功能

● 通過柵極電阻RG控制開關速度

● 通過施加 2V VGS 和 1 mA 的正向偏置電流,對 JFET 的柵極進行過驅動,可使 RDS(on) 進一步降低10–15%

● 可選通過 JFET 柵極控制開關速度

● 支持多 FET 器件并聯

● 更適合低速開關應用

SiC Cascode JFET

● 常閉型

● 極低導通電阻 RDS(on),關斷損耗極小

● 在 0V 時可作為電壓阻斷器

● 柵極驅動電壓范圍:0V至+12V,或使用緩沖電路時-5V至+20V(-3V至+18V時可實現最佳MOSFET性能)

● 可使用市售柵極驅動器,實現更靈活的柵極驅動

● 可通過外部 RG 控制開關速度(有一定開關損耗),或使用緩沖電容 C 控制

● 具備優異的 MOSFET 體二極管特性,正向壓降 VF 極低,反向恢復電荷QRR 極小

● 更適合高頻開關應用

SiC MOSFET

● 常閉型

● 低導通電阻 RDS(on)

● 便于并聯與速度控制

● 不具備溫度自監測功能

在某些應用場景中,讓半導體器件處于常開狀態更為便利。右側的電路圖展示了一個典型示例:通過簡單的過驅動方式實現可雙向阻斷的直接驅動電路。在此電路中,由于器件處于常開狀態,即使沒有柵極驅動電源,每個JFET也處于導通狀態。利用市售的柵極驅動器可直接驅動每個JFET的柵極。

此處,每個JFET的開爾文源極端子與柵極驅動器的公共引腳 COM 相連,JFET的導通通過一個大阻值的柵極電阻 RODV 實現,無需外部電壓調節。可以將 RODV 視為與 JFET 的柵-源二極管協同工作,共同構成其自身的穩壓器。

假設在該電路中,柵極驅動器供電電壓 VDD 和 VSS 為±15V,柵極電阻 RODV 取值為1kΩ。當柵極電流處于毫安量級時,JFET 的柵-源電壓 VGS 在室溫條件下約為2.3V。柵極驅動電流可通過以下公式進行近似計算:

柵極驅動電流約為12.5 mA,即每個JFET柵極約6.25 mA。由此可得,柵極驅動的功耗為15 V × 12.5 mA = 0.19 W。正是如此低的功耗,既實現了更低的導通電阻(RDS(on)),又保證了良好的片上溫度檢測功能。僅需1 mA的電流就足以對JFET柵極提供正向偏置,進一步降低RDS(on);而進行溫度檢測時,也僅需5至10 mA的電流即可輕松實現。

與包括SiC MOSFET和超結(super-junction,SJ)MOSFET在內的所有其他半導體技術相比,安森美(onsemi)第四代SiC JFET和Cascode JFET,是迄今為止在任何給定擊穿電壓下最接近理論最小導通電阻(即所謂的單極極限)的器件。

這主要得益于安森美革命性的半導體制造工藝。通過采用自對準溝槽溝道(self-aligned trench channel)制造技術,柵極結構能夠自動與源極和漏極精確對齊,從而有效縮小漂移區。正是這種制造工藝,使得器件具備了低導通電阻(RDS(on))、高阻斷電壓、更強的電流承載能力以及更快的開關速度,同時還擁有正溫度系數,便于并聯使用。

垂直型JFET截面圖

極低的單位面積導通電阻SiC JFET帶來的最具影響力的優勢或許是降低總成本,這主要源于兩個關鍵因素:更小的PCB占用面積和發熱量大幅減少。這一優勢使SiC Cascode JFET相比SiC MOSFET具有巨大優勢。

SiC JFET的單位面積導通電阻(RDS(A))約為SiC MOSFET的一半,僅為低壓硅(Si)MOSFET的約10%。這不僅提升了系統性能,也帶來了成本優勢。

在對比導通電阻隨溫度變化的曲線時,盡管第四代(Gen4)SiC JFET的電阻-溫度曲線斜率比某些其他工藝更陡,但其 RDS(A) 的優勢仍然超過2倍。

第一象限開關時序

由于JFET是常開型器件,需要對柵極驅動施加負電壓才能將其關斷并阻斷高壓(包括電壓尖峰)。在所謂的JFET工作“第一象限”期間,當電壓向0V增加時,器件開始導通。施加正的漏源電壓 VDS 會使漏極-柵極PN結反向偏置,導致其耗盡區擴展。如果 VDS 持續增加,直至耗盡區填滿整個溝道,JFET將進入“飽和”狀態,溝道被“夾斷”,電流不再隨 VDS的增加而增大。

施加正的柵源電壓(VGS)會使漏極-柵極和柵極-源極之間的PN結處于正向偏置狀態,導致耗盡區收縮并抑制其擴展。正如我們將看到的,根據工作條件的不同,施加正的 VGS 是降低導通電阻的簡易方法。

由于SiC JFET的柵極由柵極-源極和柵極-漏極之間的PN結構成,無需額外的柵極氧化層屏蔽結構。這不僅避免了增加導通電阻,還從根本上消除了柵極氧化層的可靠性問題。此外,JFET不存在漏極-源極輸出電容,其全部輸出電容都存在于漏極與柵極之間,因此有:COSS = CRSS。這一特性使得JFET的開關速度可以通過簡單調節柵極電阻(RG) 來精確控制。

下方圖表展示了安森美UJ4N075004L8S SiC JFET在25°C環境溫度(上圖)和175°C(下圖)下的輸出特性曲線。當柵源電壓 VGS 為 -5 V 時,其溝道寬度被耗盡區完全夾斷,器件處于完全飽和狀態,電流受到限制。

將 VGS 提升至-4V可使耗盡區收窄、導電溝道變寬,從而增加導電性并降低導通電阻。在此“Active”區內,增大 VDS 會擴展耗盡區,但此時電流隨 VDS 的增加已不再顯著上升,導致輸出特性曲線發生彎曲。

圖表中藍色虛線左側區域對應所謂的“ohmic ”區,該區域右側藍線之外才進入“Active”區或線性區。在“ohmic ”區內,隨著柵源電壓 VGS 的升高,電導率增加,電阻下降。當 VGS 達到 0V 時,JFET 完全導通,漏極與源極之間的電流溝道完全開啟。若在此基礎上將 VGS 繼續提升約2V,導通電阻 RDS(on) 可進一步降低達 15% 。

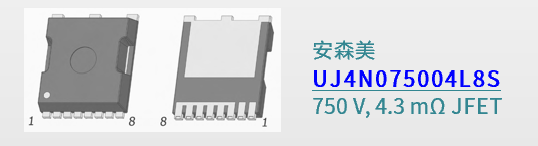

安森美UJ4N075004L8S 750 V, 4.3 mΩ JFET

最大化JFET開關效率

第三象限開關時序

在過去,JFET沒有固有體二極管常被視為一種缺陷。但在現代功率應用中,這反而成了一項優勢——盡管要充分發揮這一優勢需要一定的設計技巧,尤其是在反向導通階段,即工程師所稱的“第三象限”操作中。

上方的一組平面示意圖展示了一個處于反向偏置狀態的安森美第四代 JFET,其柵源電壓 VGS 為 -15V。雖然該 JFET 在第一象限可阻斷數百伏電壓,但其在第三象限的阻斷電壓能力相對有限,更多取決于漏極-柵極二極管與柵極-源極二極管的偏置狀態,而非溫度。左圖中,漏源電壓 VDS 為 -3V。

此時 VGS 與 VDS 之間的差值為 -12V,低于閾值電壓 VG(th) ,因此溝道完全阻斷,無源極-漏極電流通過。當 VDS 降至 -9V 且差值減小至 -6V 時,溝道略微開啟,允許微小電流通過。在右圖中,當差值達到 -4V(超過閾值電壓2V)時,源極-漏極電流得以更自由地流動。

當 VDS 低于閾值差值時,JFET 在第三象限的阻斷能力通常受限,而這也正是 JFET 快速開關能力發揮作用之處,該特性使得“死區時間”能被盡可能縮短。

片上溫度檢測由于JFET的柵源電壓 VGS 會隨溫度變化,因此向柵極注入一個微小的正向偏置過驅電流(范圍在1 mA至5 mA之間),即可通過外部電路(例如放大器)輕松測量JFET的結溫 TJ 。該過驅電流會在柵源之間的二極管上產生一個壓降,而此壓降能以高度可預測的方式反映結溫 TJ 。通過測量 VGS 壓降,即可依據公式推導出 JFET 的溫度。

類似地,利用結溫 TJ 作為關鍵變量,通過測量漏源電壓 VDS 即可獲得可靠的電流值。該方法采用兩個相同的高壓阻斷二極管 D1 和 D2 ,與 JFET 的漏極串聯連接。當結合使用柵極驅動器退飽和保護(DESAT)引腳時,可經由這兩個二極管提供一個微小電流(范圍在毫安至微安級別)。或者,也可從柵極驅動電源通過一個電阻提供該小電流。

在這兩種情況下,您都需要對二極管 D1 進行鉗位,并跨接一個放大器,以測量該二極管兩端的壓降。此壓降即代表 JFET 的漏源電壓 VDS 。既然已知芯片溫度就能輕松估算其導通電阻 RDS(on) ,您便可直接運用歐姆定律來估算漏極電流,而無需使用額外的傳感器:

隨著裸芯尺寸不斷縮小,以及單位面積導通電阻 RDS(A)(即每單位面積的 RDS(on))持續降低,確實會帶來熱管理方面的挑戰。安森美通過在其制造工藝中引入銀燒結(silver sintered)裸片貼裝技術來應對這一挑戰,替代傳統的含鉛焊料貼裝方式。銀燒結材料的熱導率最高可達傳統焊料的六倍。

左側重疊的陰影矩形代表三款安森美器件在印刷電路板(PCB)上所占用的相對面積:第四代 750 V SiC JFET(藍色)、第四代 750 V SiC MOSFET(深灰色)和第三代 650 V SiC MOSFET(淺灰色)。盡管第四代 MOSFET 的芯片面積比 JFET 大出 40%,其導通電阻反而略高,且結到外殼的熱阻 RθJC 也稍大——這正是由于該 MOSFET 仍采用傳統的焊料貼裝工藝所致。當然,更小的裸片尺寸確實也影響了結到環境的熱阻 RθJA ,尤其是封裝外殼到周圍環境散熱的角度。

未完待續,后續推文將介紹SiC Cascode JFET等特性。

評論