激光芯片為AI數據中心帶來多路復用

隨著 AI 數據中心對帶寬和功耗的需求不斷提升,網絡架構正從電氣互聯向光電互聯大規模演進。但在共封裝光學(CPO)方案中,一直缺少一個關鍵組件 —— 集成化的激光器。如今,這一空白被填補:Tower Semiconductor 與 Scintil Photonics 聯合宣布,已量產全球首款面向 AI 基礎設施的單芯片密集波分復用(DWDM)光引擎。該技術通過單根光纖傳輸多路光信號,大幅降低功耗與延遲,實現數十個 GPU 之間的高效互聯。

光學復用:并非新技術,卻適配 AI 新需求

Scintil Photonics 首席執行官馬特?克勞利(Matt Crowley)表示,光學復用技術并非新鮮事物,其發展與互聯網幾乎同步。上世紀 90 年代,電信運營商在全球鋪設了大量光纖,最初僅計劃單根光纖傳輸單路波長信號;而當行業發現可通過復用技術在單根光纖上傳輸數十路波長時,徹底革新了通信行業。

但 DWDM 技術遲遲未能落地 AI 數據中心,核心原因是成本與規模化應用的矛盾。克勞利指出:“AI 數據中心的數據傳輸規模堪比超級計算機的擴容,尤其是scale-up 網絡(機架 / 集群內加速器直連),需要實現數十個 GPU 與內存的無縫協同,對帶寬和超低延遲的要求極高。”

此前,網絡工程師已在scale-out 網絡(數據中心內集群間互聯)中用光電互聯替代了銅纜,而當前的技術焦點正轉向 scale-up 網絡,推動光學組件與處理器同封裝(共封裝光學,CPO)。克勞利表示:“頭部芯片企業都在嘗試將光學芯片與 GPU 封裝,但由于無法將激光器集成到硅工藝流中,一直無法實現單芯片多波長傳輸。”Scintil 與 Tower 將在 3 月 17-19 日洛杉磯舉辦的 OFC 2026 大會上公布制造路線圖與技術細節。

面向 AI 網絡的集成光子技術

Scintil 的SHIP 技術(Scintil Heterogeneous Integrated Photonics,異構集成光子)將激光器、光電二極管、調制器等組件集成到量產硅晶圓上。克勞利將其稱為 “硅基光子版的 CMOS 工藝”,核心突破在于解決了光學增益材料與硅基底結合的固有難題。

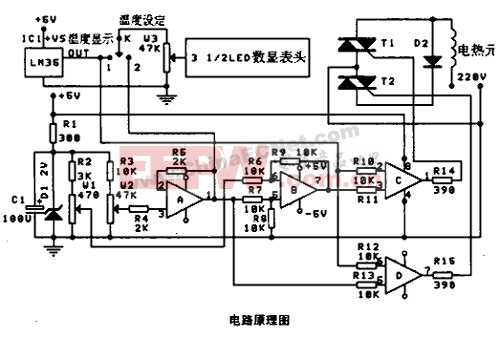

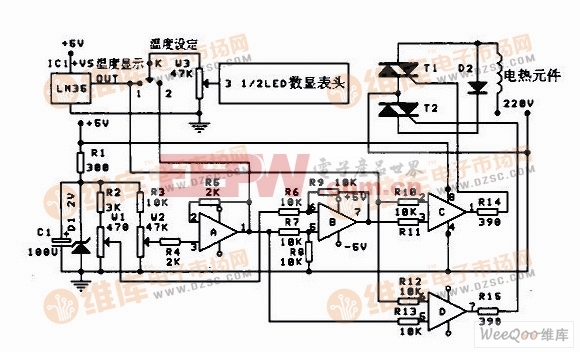

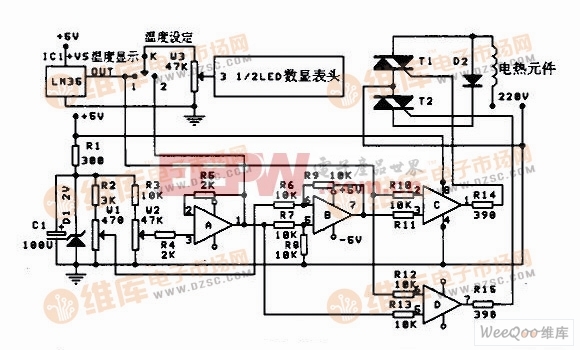

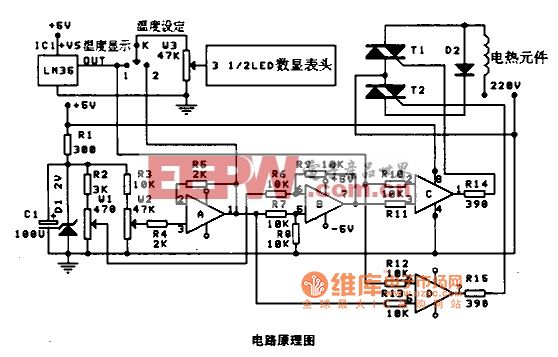

制造流程

采用 Tower Semiconductor 的 300 毫米硅光子晶圓,完成無源光學組件制備;

晶圓倒裝暴露掩埋氧化層,將未圖案化的 InP/III-V 半導體芯片精準鍵合至激光位點,最大限度減少昂貴材料的使用;

通過光刻工藝蝕刻衍射光柵,集成 8 個分布式反饋(DFB)激光器。

克勞利強調:“我們并非重新發明激光器,而是通過先進光刻技術,實現了比傳統硅工藝更精準的波長間距與穩定性。”

最終產品為LEAF Light光子集成電路,集成兩組 8 通道 DFB 激光陣列。單光纖端口可傳輸 8/16 路波長(通道間隔 100/200GHz),避免信號串擾與模式跳變;配套 ASIC 芯片負責激光陣列的控制與監測。

多波長激光器推動共封裝光學升級

克勞利表示:“這是首次將激光器直接集成到 CPO 芯片中。” 英偉達、博通已推出單波長 CPO 方案,驗證了其在 scale-out 網絡中的可行性,而 Scintil 的技術將推動下一代 scale-up 網絡的 CPO 升級。

單根光纖傳輸多路波長,構建了 “低速寬頻” 的高效架構:例如,不再用單通道傳輸 400Gb/s,而是將 50Gb/s 分配到 8 個通道,單光纖數據速率最高可達 1.6Tb/s,功耗效率大幅提升。英偉達的路線圖顯示,未來 DWDM 互聯有望實現每比特低于 1 皮焦耳的能耗。

核心價值:降低延遲

克勞利認為,延遲優化是該技術最關鍵的優勢:“GPU 之間必須保持低延遲,否則處理器運算速度快于網絡,會導致 GPU 長期等待數據,數十 / 數百個 GPU 組成的 scale-up 網絡中,這一問題會被放大。” 高速通道的前向處理與糾錯會進一步犧牲延遲,導致 GPU 利用率大幅下降;而多波長 DWDM 技術可將 GPU 利用率提升一倍。

量產與商業化規劃

Scintil 與 Tower 計劃在 2026 年底向客戶交付數萬套產品,2027 年產能提升一個數量級;到 2028 年,客戶將在 scale-up 網絡中部署 DWDM 技術,屆時供應鏈將完全就緒。克勞利表示:“這項技術將為 AI 數據中心打開全新的可能性。”

評論