雷達(dá)系統(tǒng)中的電源噪聲:如何通過高抑制比設(shè)計優(yōu)化射頻轉(zhuǎn)換器性能?

引言

本系列的第 1 部分介紹了噪聲如何耦合到模數(shù)轉(zhuǎn)換器 (ADC) 電源、噪聲如何通過ADC 電路進(jìn)行耦合以及一些常見的電源權(quán)衡因素。現(xiàn)在,我們將運用這些知識來測量ADC12DJ5200RF ADC 的噪聲和雜散抑制,即電源抑制比 (PSRR) 或電源調(diào)制比(PSMR)。

文中通過示例說明 ADC 電源引腳耐受的噪聲大小,從而幫助您在下一個信號鏈設(shè)計中適當(dāng)縮小適用電源管理器件的選擇范圍。此外,還介紹了一些實用的設(shè)計指南。

測量 PSRR 或 PSMR

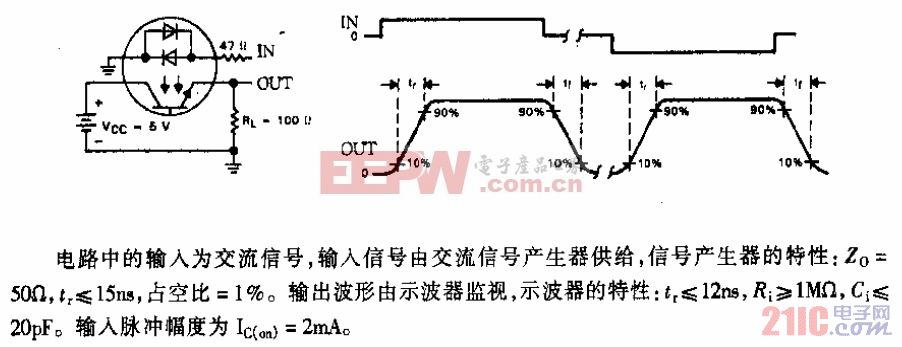

圖 1 展示了使用偏置 T 單獨測試 PSRR 或PSMR 電源節(jié)點的測量設(shè)置。偏置 T 買來即用,可將交流和直流信號合并至單個被測電源。偏置 T 必須具有足夠高的額定電流以提供足夠的偏置;否則,測量結(jié)果可能會不可靠 。

圖 1 用于 PSRR 或 PSMR 測量的工作臺測試設(shè)置

PSRR 測量步驟:

上下滑動閱讀

正常設(shè)置評估模塊或系統(tǒng)板,然后隔離被測電源。這可能需要移除特定電源域的去耦電容器。

對該電源域應(yīng)用偏置 T,同時使用干凈的外部工作臺電源設(shè)置適當(dāng)?shù)闹绷麟妷骸?/p>

使用數(shù)字萬用表確認(rèn)被測電源的測試點盡可能靠近ADC(例如靠近電源引腳),從而確保按照數(shù)據(jù)表中的標(biāo)稱值施加適當(dāng)?shù)闹绷麟妷骸?赡苄枰晕⒄{(diào)整工作臺電源以補償偏置 T 和電纜損耗。

為 ADC 的其余部分和電路板電源供電,保持這些電源處于標(biāo)稱值。在第一奈奎斯特區(qū)域內(nèi)選擇一個合適的頻率(本例選擇從 10MHz 開始),并將正弦波信號源注入偏置 T。該信號源被稱為誤差信號。

從低幅度信號開始,慢慢提高幅度,直到本底噪聲產(chǎn)生雜散,同時使用 TI 的高速數(shù)據(jù)轉(zhuǎn)換器專業(yè)軟件(HSDC-Pro)[2] 來顯示并測量數(shù)字輸出快速傅里葉變換 (FFT) 頻譜。誤差雜散在 FFT 頻譜中應(yīng)足夠高且可重復(fù),在注入的誤差測試頻率 (10MHz) 下很明顯。在本例中,捕獲的誤差雜散幅度為 –78dB。下頁中的圖 2 展示了從輸出頻譜產(chǎn)生的注入誤差信號示例。

用示波器或頻譜分析儀記錄注入的誤差信號電平。然后,在 ADC 的被測電源節(jié)點(最好是 ADC 的電源引腳)附近再次測量誤差信號電平。記錄在該引腳處注入的電壓峰-峰值 (VPP) 信號,由此可以通過簡單的數(shù)學(xué)公式計算得出 PSRR。例如,如果測量到應(yīng)用的誤差信號為 8mVPP,而 ADC的滿量程電壓為 0.8VPP,則只需取這兩個數(shù)字的比值,即 20 × log(8mV/800mV) = –40dB。若要計算PSRR,從先前在 FFT 頻譜中確定的誤差雜散幅度中減去這個數(shù)字,即 PSRR:–78dB – (–40dB) =–38dB。

至少在 ADC 的第一奈奎斯特區(qū)域上測量各種誤差信號注入電平和頻率。

對 ADC 的其余電源節(jié)點重復(fù)上述步驟。

圖 2:應(yīng)用了誤差信號的 ADC 輸出 FFT 頻譜

圖 3 突出顯示了 ADC12DJ5200RF 的PSRR 測量結(jié)果。VA11 和 VA19 曲線表明,由于內(nèi)部 ADC 電路拓?fù)洳煌珹DC 模擬電源的穩(wěn)健性會不如數(shù)字電源 (VD11),并且更容易產(chǎn)生電源噪聲,如第 1 部分文章中所述。此外,PSRR 通常會使性能降低,應(yīng)用的頻率越高,越接近奈奎斯特或 fS/2 區(qū)域。這有助于深入了解 ADC 的電源電路設(shè)計,凸顯了解低壓降穩(wěn)壓器 (LDO) 或轉(zhuǎn)換開關(guān)的噪聲分布的重要性。在許多情況下,噪聲分布被認(rèn)為是“白噪聲”,或在整個頻率范圍內(nèi)是平坦的,這是應(yīng)該確認(rèn)的一點。

圖 3:ADC12DJ5200RF PSRR 與每個電源域

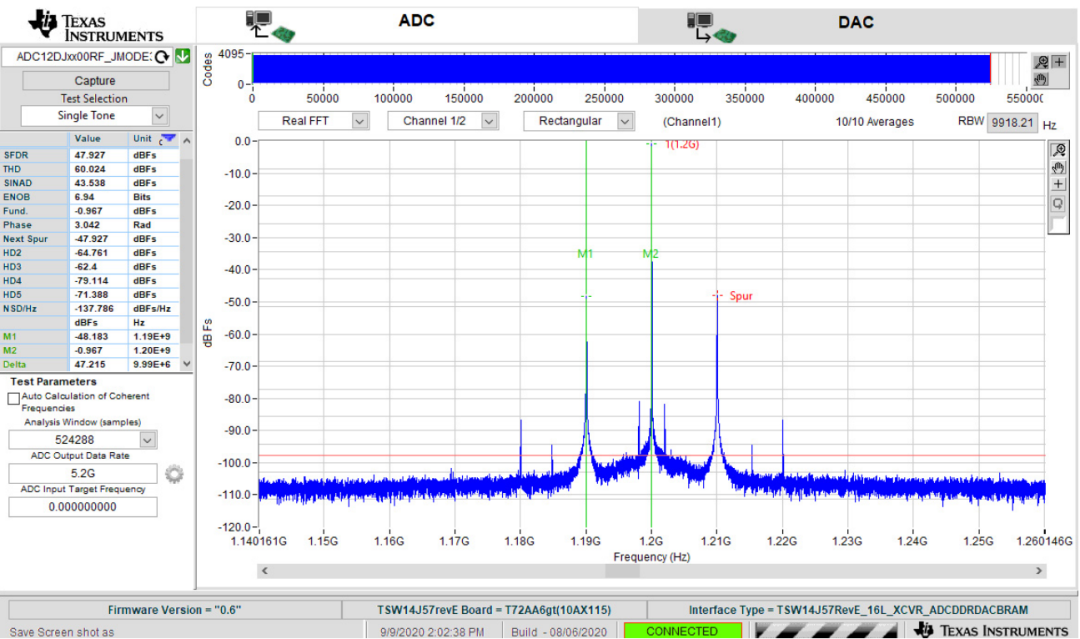

PSMR 是在 ADC 電源引腳處注入的電源噪聲與 ADC 模擬輸入端施加信號的調(diào)制幅度之比。測量 PSMR 的技術(shù)與 PSRR 類似,不同之處在于 PSMR 的測量是將電源噪聲或雜散與施加到 ADC 的附加射頻輸入信號進(jìn)行耦合。如圖 4 所示,利用調(diào)制原理,在電源引腳上施加 10MHz 誤差信號將調(diào)制到射頻輸入信號上,并在射頻輸入頻率加上或減去誤差信號頻率(fIN + fError,即 1.2GHz ±10MHz)附近產(chǎn)生調(diào)制分量。

若要計算 PSMR,先查看圖 4 所示的fIN - fError (1.2GHz – 10MHz) 的幅度,為–48.13dBFS。如果施加到電源引腳的誤差信號 (fError) 約為 100mVPP 且 ADC 的滿量程電壓為 0.8VPP,則只需取這兩個數(shù)字的比率,即 20 × log(100mV/800mV) = – 18dB,然后從 FFT 頻譜中的調(diào)制幅度減去該數(shù)字,即PSMR:–48dB – (–18dB) = –30dB。

圖 4:應(yīng)用了強(qiáng)制誤差信號的 PSMR 示例

LDO 和直流/直流轉(zhuǎn)換器之間的主要區(qū)別在于電壓轉(zhuǎn)換所需的開關(guān)機(jī)制。直流/直流轉(zhuǎn)換器被認(rèn)為噪聲更大,因為它們會產(chǎn)生諧波和紋波。在對噪聲敏感的應(yīng)用中,通常建議將 LDO用于敏感電源,但隨著電源集成電路 (IC) 設(shè)計的改善,新的直流/直流轉(zhuǎn)換器會非常接近 LDO 的噪聲性能。

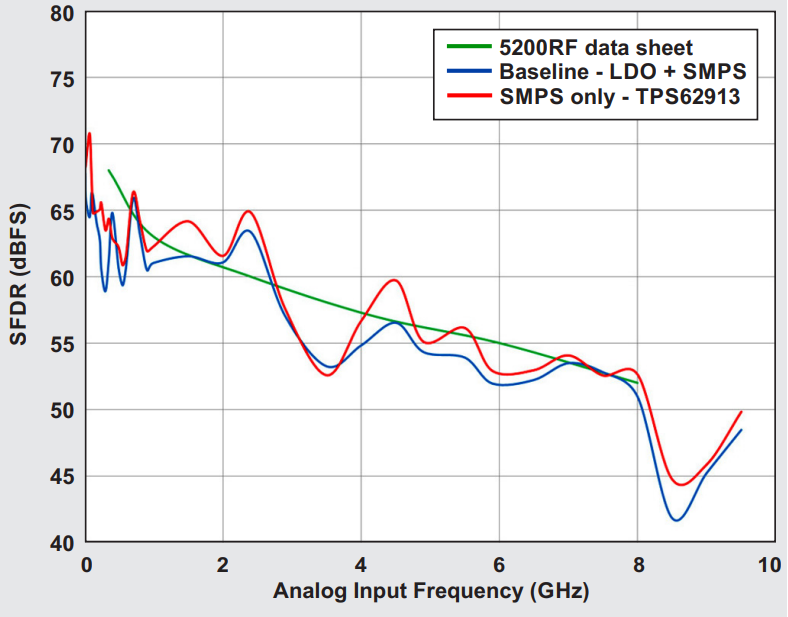

圖 5 比較了基于 LDO 的電源設(shè)計(LDO + 開關(guān)模式電源 [SMPS])與基于直流/直流轉(zhuǎn)換器的電源(僅SMPS)。這兩條曲線展示了將 1.5GHz 模擬輸入頻率應(yīng)用到 ADC12DJ5200RF ADC 的情況,并使用平均 FFT數(shù)據(jù)來比較性能的不同。與 SMPS (TPS62913) 設(shè)計相比,LDO 的基頻 (1.502GHz) 附近沒有明顯的電源調(diào)制信號。

圖 5.1.502GHz 輸入信號附近的 PSMR 比較

直流/直流轉(zhuǎn)換器通常在 20kHz 左右至 2MHz 的頻率下進(jìn)行開關(guān),因此在 FFT 輸出頻譜中接近 DC (0Hz)的開關(guān)頻率處也會出現(xiàn)開關(guān)雜散。

圖 6 展示了頻譜中 DC 附近的放大版曲線,并將直流/直流轉(zhuǎn)換器性能與基于 LDO 的電源設(shè)計進(jìn)行了比較,沒有降低 ADC 性能的明顯雜散。在考察 ADC 性能時,無雜散動態(tài)范圍 (SFDR) 是一個重要參數(shù)。除了基頻之外,SFDR 是 ADC 頻譜中存在的最高雜散。最高雜散通常與諧波相關(guān),但也可由開關(guān)雜散決定。在任一種情況下,由電源或其他耦合噪聲引起的雜散都會使 ADC 的 SFDR 性能降低。

圖 6.DC 處的 PSMR 比較

圖 7 比較了從近 DC 到近 10GHz 的幾個頻率點上的SFDR 性能。SMPS(直流/直流轉(zhuǎn)換器)設(shè)計的 SFDR 性能與 LDO + SMPS 設(shè)計的 SFDR 性能相當(dāng)。

圖 7.SFDR 比較

慎重的做法是,比較這兩種設(shè)計的信噪比 (SNR)。電源噪聲可能表現(xiàn)為基頻附近不必要的調(diào)制信號,或者也可能出現(xiàn)在 DC 附近并影響 ADC 的 SNR 性能。圖 8 比較了兩種電源設(shè)計之間的 SNR 性能。同樣,SMPS(直流/直流轉(zhuǎn)換器)設(shè)計與 LDO + SMPS 設(shè)計的 SNR 性能相當(dāng)。

圖 8.SNR 比較

綜合考量

鑒于 PSRR 和 PSMR 指標(biāo)對 ADC 性能的影響,以下示例展示了如何為您的下一個電源設(shè)計選擇 LDO 或SMPS。

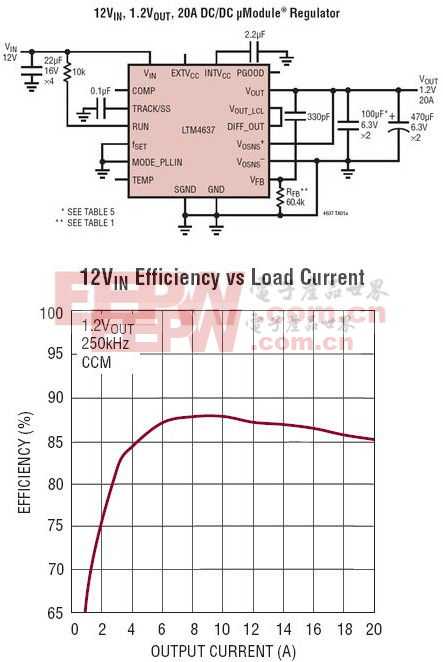

以 TPS62913 降壓轉(zhuǎn)換器為例,數(shù)據(jù)表顯示,正確使用 LC 濾波時,轉(zhuǎn)換開關(guān)電路將在 100kHz 帶寬上具有綜合積分噪聲和 18.3μVRMS 的輸出電壓紋波。假設(shè)噪聲為高斯噪聲,則噪聲密度為 57.8nVRMS/√ Hz。

高速 ADC 模擬電源的典型 PSRR 范圍為 –40dB至–60dB。如圖 3 所示,使用 ADC12DJ5200RF 時,對于 VA11,該電源在奈奎斯特或 fS/2 區(qū)域中的 PSRR 平均值為 –40dB (10mV/V)。可以測量或使用公式 1 計算ADC 的本底噪聲。ADC12DJ5200RF 是一款 12位、5.2GSPS (fS) ADC,在第一奈奎斯特區(qū)域采樣時具有0.8VPP 的差分輸入滿量程范圍 (FSR) 和大約 54dB 的SNR,如圖 8 所示。

公式 1.

與 ADC 的本底噪聲相比,SMPS 的本底噪聲幾乎高出五倍(即 57.8nV/11.1nV)。當(dāng) ADC 的電源引腳引入噪聲(為 –40dB)時,SMPS 穩(wěn)壓器的 ADC PSRR 衰減將轉(zhuǎn)化為 578pV/√ Hz 或 57.8nV/√ Hz × 10mV/V 的卷積穩(wěn)壓器噪聲。請注意,–40dB 遠(yuǎn)低于 ADC 的本底噪聲,不會出現(xiàn)在 ADC 的輸出頻譜中,也不會降低 ADC 的交流性能。

圖 8.SNR 比較

通用電源設(shè)計概要和指南

高速、精密和射頻 IC 以及電路對開關(guān)元件大電流、輸出電容器等效串聯(lián)電阻和使用標(biāo)準(zhǔn)直流/直流轉(zhuǎn)換器設(shè)計時涉及的磁性元件所產(chǎn)生的噪聲和雜散分量很敏感。

當(dāng)處理輸入端的低噪聲問題時,需要對 ADC 的模擬和時鐘輸入(以及電路)進(jìn)行超嚴(yán)格的審查。但是,電源也是輸入。不能僅因為電源是直流偏置電路,就認(rèn)為它們不會降低射頻性能。

了解如何在電源設(shè)計分析中應(yīng)用 PSRR 和 PSMR 數(shù)值,則能夠更輕松地選擇要使用的穩(wěn)壓器技術(shù)和類型。如果找不到 ADC 的 PSRR 數(shù)值,可在 TI 的 E2E? 技術(shù)支持問題中請求此信息,或使用本文中概述的指南來測量 PSRR。

為任何高速或精密 ADC、射頻或噪聲敏感型 IC 設(shè)計電源域時,可參考下列一些技巧來強(qiáng)化抑制電源噪聲的設(shè)計:

? 對系統(tǒng)電路板上和 ADC 及其周圍的所有電源軌和總線電壓進(jìn)行解耦。

? 切記,每個附加的濾波級均可增加大概 20dB/十倍頻程的噪聲抑制。

? 對高頻和低頻進(jìn)行解耦,這可能需要多個電容值。

? 在電源入口點處(就在去耦電容器接地之前)使用串聯(lián)鐵氧體磁珠,無論系統(tǒng)電路板的每一個電源電壓是來自 LDO 還是 SMPS。

? 為了增加電容,請使用緊密堆疊的電源平面和接地平面對(間距 ≤4 密耳),這一做法的目的是向印刷電路板設(shè)計添加固有的高頻 (>500MHz) 去耦功能,而且沒有成本。實施良好的布局分區(qū)。使有噪聲的電源遠(yuǎn)離敏感的模擬電路,如 ADC 的前端級和時鐘電路。

? 在 PCB 的另一側(cè)放置一些大電流磁性元件,以增加隔離效果。

? 遵循 IC 制造商的建議;如果應(yīng)用手冊或數(shù)據(jù)表中沒有直接說明,請研究評估板,這是一個很好的學(xué)習(xí)工具。

上述建議可幫助提供可靠的電源設(shè)計,從而在許多應(yīng)用中實現(xiàn)數(shù)據(jù)表中指明的性能。

評論