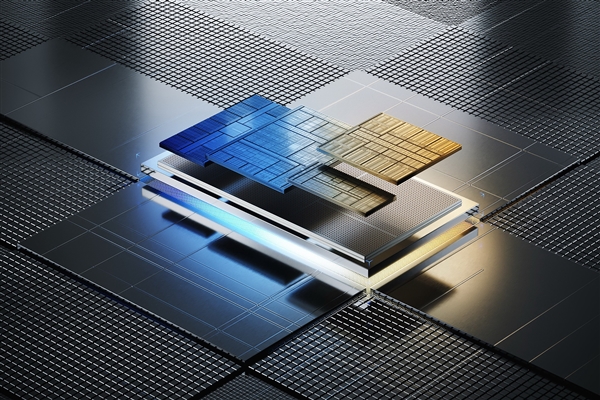

硅通孔(TSV)復雜度引發制造瓶頸

制作硅通孔是必要但極具挑戰的難題。

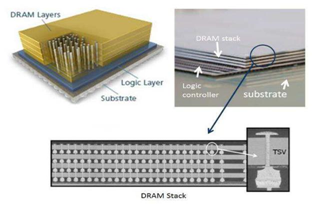

硅通孔(TSV)為高帶寬內存堆棧中的 DRAM 裸片、硅中介層以及新興 3D 芯片堆棧提供關鍵互聯。但隨著 TSV 尺寸不斷微縮,其制造成本急劇上升,且更容易出現缺陷。

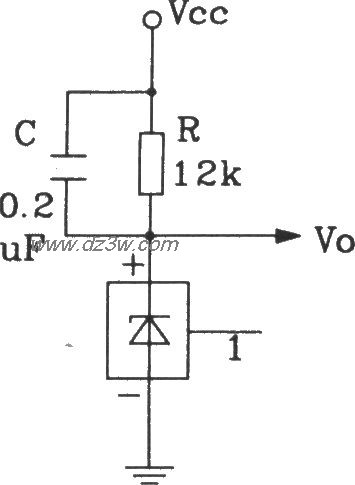

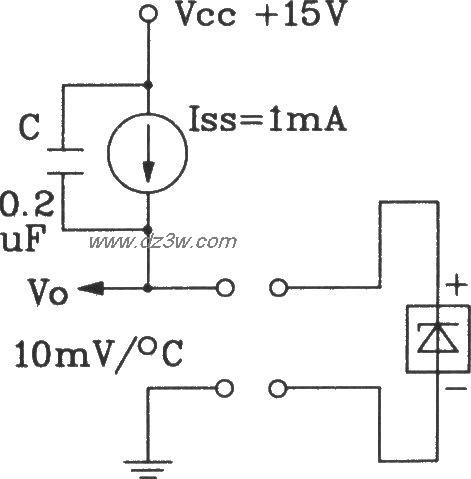

TSV 是集成 MEMS、射頻、模擬 IC、GPU 等芯片的必備技術。它能提升單裸片性能,作為高頻電信號的垂直傳輸線,優化多裸片系統表現。但隨著器件密度提升,TSV 密度也隨之增加,進而要求通孔間距更小、TSV 尺寸與微凸點更小。這會引發信號完整性問題,需要全新屏蔽方案,并加速向混合鍵合過渡。

目前,全球僅有少數企業具備先進封裝與組裝能力。AI 熱潮導致 HBM(及其他主流存儲)缺貨,可生產搭載 TSV 的 2.5D/3D 系統的先進封裝產能,遠跟不上需求爆發式增長。

TSV 可在制造流程的先、中、后三個階段制作,這通常決定了由誰整合工藝。例如,日月光、安靠等 OSAT 廠商通常采用TSV 后制程(露孔工藝);臺積電、三星等晶圓廠則采用TSV 先制程與中制程;英特爾代工服務則在中介層與嵌入式芯片平臺均支持 TSV 集成。

TSV 的尺寸跨度極大:

2nm 及以下工藝使用nanoTSV(<100nm),為晶體管供電軌提供更高效供電。

硅中介層中的 TSV 直徑可達5–20μm,深度80–120μm,貫穿減薄后的硅片,通過焊球連接上方芯片或下方 PCB。

TSV 對機械應力敏感,需要設置禁布區(keep-out zones) 限制通孔間距。高深寬比結構易產生空洞、接縫等缺陷,需要優化刻蝕與電鍍工藝以保證良率與長期可靠性。

下文將解析 TSV 制造為何如此困難,以及如何降低成本。

TSV:特殊的銅互聯

TSV 技術起源于約 20 年前,東芝率先將其用于 CMOS 圖像傳感器,爾必達將其用于手機 DRAM。相比傳統引線鍵合與倒裝凸點,TSV 連接更優,且屬于芯片級封裝延伸,不會增大封裝體積。

TSV 逐步應用于 CMOS 圖像傳感器、FPGA、HBM 堆棧、傳感器、MEMS / 邏輯、射頻模塊、緩存 / 處理器堆棧,并即將用于光子 IC 與電子 IC 互聯。

HBM 是最受關注的 TSV 應用場景,美光、SK 海力士、三星均在內部完成 TSV 制程。HBM 內部 TSV 直徑通常2–5μm,深度30–60μm,采用TSV 中制程(前道器件后制作通孔),在密度、成本、熱約束間取得最佳平衡。TSV 呈規則陣列排布,避開模擬與高應力區域。

硅中介層同時通過 TSV 實現垂直連接,通過重布線層(RDL)實現水平連接。其中 TSV 尺寸大于 HBM,直徑5–20μm、深度80–120μm,成簇分布在微凸點陣列下方、布線通道、裸片邊緣與供電區域。晶圓廠負責硅中介層制造,少數專業廠商提供中介層服務,但具備先進能力的極少。AI 擴張帶來的壓力正沖擊整條供應鏈,并將推動未來變革。

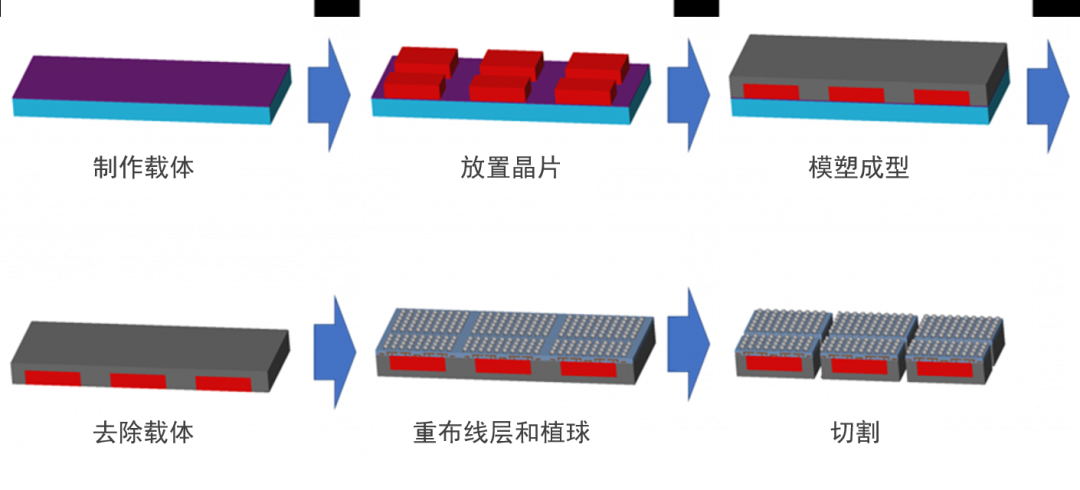

TSV 制造流程

TSV 制造每一步都至關重要,其中幾項挑戰尤為突出:

刻蝕:尺寸微縮使深孔底部殘留物更難清除,同時要保持近乎垂直的輪廓。輪廓決定氧化襯層、阻擋層、銅種子層的附著與共形性,頂部收口會形成空洞,威脅可靠性。

銅電鍍:理想為自下而上填充,需要精準控制藥液。

化學機械拋光(CMP):去除頂部多余銅。

TSV 露孔:最關鍵的最后一步。晶圓臨時鍵合在載體上后,經粗磨、中磨、精磨,再用 CMP 接近通孔,最終通過等離子刻蝕露出 TSV。

安靠高級 3D 產品總監里克?里德表示:干法刻蝕對硅片損傷小,晶圓在刻蝕前已打磨至鏡面,保障表面質量。

精準的 TSV 露孔流程包括:

標定博世刻蝕形成的 TSV 深度

均勻涂布鍵合膠與解離層,烘烤固化后鍵合

背面減薄至 TSV 底部數微米內

多階段 CMP

等離子刻蝕露出 TSV

沉積氮化硅拋光停止層

沉積厚二氧化硅

CMP 至 TSV 露出

露孔后,TSV 仍由氧化襯層保護,避免金屬接觸空氣。隨后沉積氮化硅鈍化,再覆蓋厚氧化層,經 CMP 后露出與鈍化層共平面的銅 TSV,形成可加工的平坦表面。

晶圓減薄優化中,臨時鍵合材料選擇至關重要,需考慮熱預算、解離方式、與薄膜兼容性。前沿技術傾向機械與激光解離。

減薄的關鍵指標是總厚度變化(TTV),低于 5% 對堆疊與陣列至關重要,超標會導致鍵合不均、黏附失效或分層。

詳細制程步驟

圖形化與刻蝕圓柱形深孔

博世深反應離子刻蝕(DRIE)形成各向異性溝槽

PECVD 沉積氧化硅襯層,防止銅污染硅片

PVD/ALD 沉積 TaN/TiN 阻擋層

沉積銅種子層

電化學沉積(ECD)銅,無空洞填充

CMP 拋平頂部多余銅

沉積焊球或重布線層

缺陷防控

高寬比(>10:1)TSV 易出現兩類缺陷:

TSV 頂部損傷

側壁條紋

這會降低金屬填充質量與電學性能。泛林研究表明,縮短預涂層時間、降低偏壓可消除頂部損傷;低壓、高壓強可抑制側壁條紋。

電鍍后銅空洞會導致電阻升高、機械強度下降甚至失效。其他常見缺陷:圖形對準偏差、沉積不均、填充不完整,均影響性能與可靠性。

邊緣缺陷是晶圓減薄最受關注的問題,微小缺陷即可導致晶圓斷裂。

應力管理

硅(2.8 ppm/°C)與銅(17 ppm/°C)熱膨脹系數失配會產生機械應力。工程師通過仿真建模、拉曼光譜、X 射線衍射、有限元分析(FEA)評估應力分布,設置禁布區避免影響有源器件。

設計軟件需集成應力與熱仿真,多芯片模塊需經過嚴格應力與疲勞測試。

納米 TSV(nanoTSV)

三大晶圓廠(英特爾、臺積電、三星)正為 2nm 及以下工藝研發背面供電架構,將供電與信號線分離,可降低30% 功耗,減少電壓跌落與 RC 延遲,釋放正面布線資源,節省光刻成本。

背面供電有三種技術路線,復雜度逐級提升:

最激進:器件制作前在環繞柵極間制作 nanoTSV

中等:電源通孔連接背面供電網絡與正面接觸層

最保守:供電線跨已制成器件

最大挑戰是背面與正面圖形互聯的套準精度。比利時微電子研究中心(Imec)提出自對準狹縫 nanoTSV 方案,實現約 100nm 套準裕度,可避免高階光刻校正,降低成本。

結論

HBM 廠商、頭部晶圓廠與 OSAT 均在芯片與模組生產的不同階段提供 TSV 制造能力。隨著 HBM 中 DRAM 晶圓持續減薄,需要更多、更小的 TSV 支撐存儲單元增長。

硅中介層 TSV 布局更靈活,以連接為目標,可加入虛擬 TSV 平衡應力。

nanoTSV 則為背面供電提供前后側關鍵互聯。

無論尺寸與應用如何,TSV 將長期存在,工程師正持續探索更具成本效益的制造方案。

評論