多裸片芯片設(shè)計(jì)中凸點(diǎn)與硅通孔的高效規(guī)劃方案

近年來半導(dǎo)體行業(yè)發(fā)展迅猛,尤其是高性能計(jì)算、人工智能和先進(jìn)汽車系統(tǒng)的需求持續(xù)攀升,傳統(tǒng)單裸片芯片設(shè)計(jì)已難以滿足當(dāng)下的功耗、性能、面積(PPA)指標(biāo)要求。為此,工程師們開始采用多裸片架構(gòu),將多個(gè)小尺寸裸片集成在單個(gè)封裝中。該架構(gòu)雖提升了芯片的可擴(kuò)展性與性能,卻也帶來了新的挑戰(zhàn),其中互連規(guī)劃問題尤為突出。而實(shí)現(xiàn)不同裸片間的通信,凸點(diǎn)與硅通孔(TSV)的高效規(guī)劃,是多裸片集成過程中至關(guān)重要的環(huán)節(jié)。

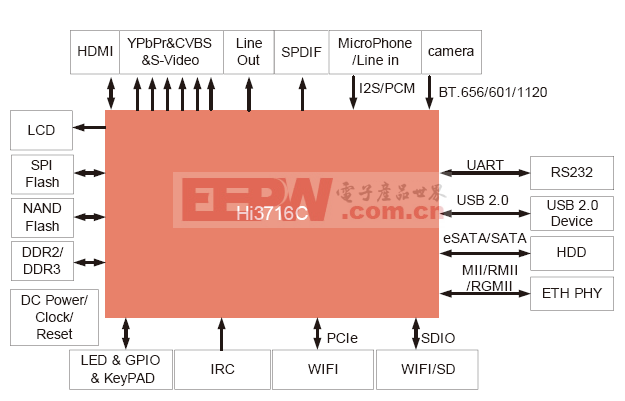

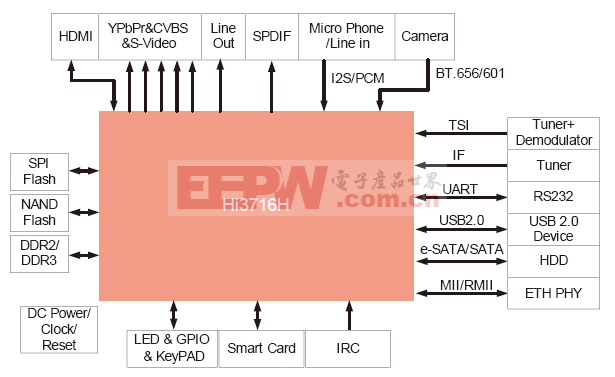

(圖 1:基于電子表格的凸點(diǎn)規(guī)劃示意圖)

在多裸片設(shè)計(jì)中,芯片間的互連通過布置在裸片表面的微凸點(diǎn)或混合鍵合焊盤實(shí)現(xiàn),這些凸點(diǎn)是裸片與中介層、襯底之間的電連接點(diǎn)。現(xiàn)代芯片設(shè)計(jì)往往需要數(shù)十萬甚至上百萬個(gè)此類連接點(diǎn),且隨著裸片數(shù)量與互連點(diǎn)的增加,規(guī)劃和管理這些連接的復(fù)雜度也會(huì)急劇上升。相關(guān)白皮書指出,不合理的凸點(diǎn)規(guī)劃會(huì)對芯片的布線可行性、布線質(zhì)量及整體設(shè)計(jì)效率產(chǎn)生負(fù)面影響。

傳統(tǒng)的凸點(diǎn)規(guī)劃依靠電子表格、繪圖軟件等簡易圖形工具人工完成,這種方式雖適用于早期僅有數(shù)千個(gè)連接點(diǎn)的單裸片倒裝芯片設(shè)計(jì),卻已無法滿足如今大規(guī)模多裸片系統(tǒng)的設(shè)計(jì)需求。人工規(guī)劃不僅耗時(shí)費(fèi)力,還極易出現(xiàn)人為失誤;此外,對某一裸片的凸點(diǎn)布局進(jìn)行修改后,往往需要對其他裸片或封裝設(shè)計(jì)做出相應(yīng)調(diào)整,若這些更新未能實(shí)現(xiàn)有效同步,后續(xù)研發(fā)環(huán)節(jié)便可能出現(xiàn)嚴(yán)重的設(shè)計(jì)錯(cuò)誤。

為解決上述問題,現(xiàn)代電子設(shè)計(jì)自動(dòng)化(EDA)工具具備了自動(dòng)化凸點(diǎn)規(guī)劃功能。設(shè)計(jì)人員可通過這類工具定義凸點(diǎn)區(qū)域 —— 即裸片上用于布置凸點(diǎn)的矩形或不規(guī)則區(qū)域,且每個(gè)區(qū)域內(nèi)的凸點(diǎn)可根據(jù)引腳間距、排布間距、對齊方式等約束條件,遵循特定模式進(jìn)行布置。完成模式定義后,軟件便能快速、精準(zhǔn)地自動(dòng)生成數(shù)千個(gè)凸點(diǎn);若區(qū)域尺寸或設(shè)計(jì)約束發(fā)生變化,凸點(diǎn)布局也會(huì)自動(dòng)更新,大幅節(jié)省設(shè)計(jì)人員的時(shí)間與精力。

信號分配是凸點(diǎn)規(guī)劃的另一核心環(huán)節(jié),每個(gè)凸點(diǎn)都必須與特定的信號、電源線或接地網(wǎng)絡(luò)相連。設(shè)計(jì)人員可手動(dòng)完成信號分配,也可借助自動(dòng)化算法,根據(jù)線長、布線效率等因素優(yōu)化凸點(diǎn)布局。自動(dòng)化信號分配能對整個(gè)多裸片系統(tǒng)進(jìn)行分析,確定信號與凸點(diǎn)的最優(yōu)映射方式,從而提升芯片整體性能,降低設(shè)計(jì)復(fù)雜度。

除凸點(diǎn)規(guī)劃外,設(shè)計(jì)人員還需對硅通孔(TSV) 進(jìn)行精細(xì)規(guī)劃。硅通孔是貫穿硅基裸片的垂直電連接結(jié)構(gòu),可實(shí)現(xiàn)信號和電源從裸片背面到正面布線層的傳輸,在多裸片垂直堆疊的 3D 堆疊芯片設(shè)計(jì)中尤為關(guān)鍵。但硅通孔的結(jié)構(gòu)尺寸相對較大,需要預(yù)留足夠的排布間距與禁布區(qū),避免對周邊電路造成損壞;若硅通孔布局不當(dāng),會(huì)減少邏輯單元的可用面積,還會(huì)對時(shí)序性能產(chǎn)生不利影響。因此,設(shè)計(jì)中必須通過精細(xì)規(guī)劃實(shí)現(xiàn)硅通孔的優(yōu)化布局,同時(shí)保證芯片的各項(xiàng)功能不受影響。

現(xiàn)代設(shè)計(jì)平臺將凸點(diǎn)與硅通孔規(guī)劃整合至統(tǒng)一的設(shè)計(jì)流程中,工程師可通過二維和三維視圖可視化展示各類連接、跟蹤工程設(shè)計(jì)變更,并執(zhí)行自動(dòng)化的設(shè)計(jì)規(guī)則檢查。借助這類工具,能在設(shè)計(jì)初期及時(shí)發(fā)現(xiàn)對齊誤差、連接缺失、信號不匹配等問題,從而避免在后續(xù)的制造環(huán)節(jié)產(chǎn)生高成本的失誤。

核心結(jié)論

凸點(diǎn)與硅通孔的高效規(guī)劃,是多裸片半導(dǎo)體設(shè)計(jì)成功的關(guān)鍵所在。隨著芯片架構(gòu)的日趨復(fù)雜,人工規(guī)劃方式已難以滿足設(shè)計(jì)需求。自動(dòng)化設(shè)計(jì)工具與規(guī)范化的規(guī)劃方法,能幫助工程師管理數(shù)百萬個(gè)連接點(diǎn)、保證設(shè)計(jì)精度,并加快產(chǎn)品的上市周期。隨著人工智能、高性能計(jì)算等先進(jìn)技術(shù)的持續(xù)發(fā)展,高效的互連規(guī)劃仍將是現(xiàn)代半導(dǎo)體設(shè)計(jì)的一項(xiàng)基礎(chǔ)要求。

評論