抑制鑒相鑒頻器中的窄脈沖

本文闡述在鑒相鑒頻器(PFD)的反饋通路中加入延遲的重要性,并分析其對電路性能的影響。

本系列上一篇文章介紹了鑒相鑒頻器(PFD)——鑒相鑒頻器(PFD)入門。該電路可同時檢測兩路輸入之間的相位差和頻率差,并具備較寬的線性相位檢測范圍。

在設計 PFD 時,在反饋通路中加入適量延遲至關重要。如果不加延遲,設計中快速的反饋環路會在電路多個節點產生過窄脈沖(即侏儒脈沖 /runt pulses)。這一點非常關鍵,因為由這些窄脈沖驅動的后級電路可能會出現工作異常。

本文將討論如何通過反饋延遲解決窄脈沖問題。為更全面地說明,我們還會分析反饋延遲對 PFD 工作帶來的不利影響。最后,在文章結尾,我們將簡要介紹 PFD 的等效狀態圖,完成對 PFD 的討論。

PFD 窄脈沖問題

圖 1 是一種常見的 PFD 實現結構,它采用兩個 D 觸發器和一個反饋結構的與門產生復位信號。

圖 1 鑒相鑒頻器

圖 2 為該 PFD 在兩路輸入(R 和 V)頻率相同但存在非零相位差時的典型波形。

圖 2 兩路輸入同頻且存在相位差時的 PFD 典型波形

在這種情況下,Dn 端會產生窄脈沖。原因是:當 Dn 變為高電平時,Up 和 Dn 同時為高,觸發復位通路中的與門。

Dn 會保持高電平直到觸發器被復位。Dn 的高電平脈沖寬度等于與門總延遲加上觸發器復位操作延遲。如果復位通路速度過快,脈沖會過窄,導致后級電路無法正常工作。因此,為保證 PFD 正常工作,必須在反饋通路中加入適當延遲。

前面討論的是 R 和 V 存在非零相位差的情況。圖 3 為相位差可忽略時的典型波形。

圖 3 R 和 V 脈沖相位對齊時的典型波形

可以看到,此時 Up 和 Dn 兩端都會出現侏儒脈沖。由于侏儒脈沖無法有效驅動后級電路,從波形可以得出結論:快速反饋通路會在鎖定點附近劣化電路性能。同樣,該問題可通過有意增加復位通路延遲、展寬輸出脈沖來解決。

值得一提的是,鎖定點附近 Up 和 Dn 出現的窄脈沖會在 VCO 控制電壓上產生紋波。不過,與其他鑒相器(如乘法型鑒相器)產生的紋波相比,這種紋波能量更低、頻譜更寬。這些特性讓紋波抑制變得容易得多。

在 PFD 反饋環路中加入延遲的影響

為理解 PFD 反饋通路中的延遲如何影響電路工作,我們分析圖 4 中的波形。

圖 4 門延遲對 PFD 波形的影響

在時刻 t=t1,檢測到 R 輸入的上升沿。假設 R 到輸出的觸發器延遲可忽略,則 Up 在 t1 同時變為高電平。

隨后在 t=t2,V 輸入出現上升沿。忽略 V 到輸出的觸發器延遲,Dn 也在 t2 變為高電平。

此時 Up 和 Dn 均為高,觸發與門在節點 A 產生復位信號。但復位脈沖變為高電平需要一定時間 —— 即與門的延遲。復位脈沖在 t=t3 變高后,觸發器還需要額外時間完成輸出復位,這一過程在 t=t4 完成。因此,圖中時長 τH 等于與門傳輸延遲加上觸發器復位輸入端到輸出端的延遲。

圖 4 底部的 Up-Dn 波形代表 PFD 的最終輸出,由 Up 減去 Dn 得到。該波形顯示,在時長 τ=τL+τH 內,最終輸出保持低電平。

這里的關鍵點是:輸出被復位后,它們不能立即響應輸入上升沿而再次變高。換句話說,τL 不能為零。原因在于,當兩路輸出在 t4 被復位時,與門需要將節點 A 的復位信號拉低,但受限于與門延遲,這一過程無法立即完成。

此外,當復位脈沖在 t=t5 變低后,觸發器需要一段額外時間從復位狀態恢復,才能準備檢測后續輸入上升沿。因此 τL 的最小值等于與門傳輸延遲加上觸發器復位恢復時間。

反饋延遲對 PFD 性能的不利影響

如上所述,圖 4 中的 Up-Dn 波形即為 PFD 最終輸出 Vout。設 τmin 為 τ 的最小值,T 為輸入信號周期(見圖 4)。此時 Up-Dn 信號的平均值最大值為:

Vout=Vdd×T(T?τmin)+0×τmin=Vdd×(1?Tτmin) 式 1

從上一篇文章已知,PFD 的增益為:

kd=2πVdd 式 2

將式 1 的平均值除以 PFD 增益,可得到 PFD 能檢測的最大相位誤差:

Δ?max=kdVout=2π×(1?Tτmin)=2π?ωR×τmin 式 3

其中 ωR 為輸入角頻率。

上一篇文章討論的理想 PFD 輸入輸出特性線性范圍為 –2π 到 +2π。而由于門電路延遲不為零,實際 PFD 無法達到這一范圍。式 3 表明,最大可檢測相位誤差取決于 ωR 和 τmin。

實例:計算含非零門延遲 PFD 的線性范圍

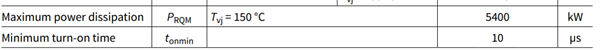

假設某 PFD 所用觸發器參數如下:

復位操作延遲:2.5 ns

復位恢復時間:3 ns

與門延遲:1.5 ns

若輸入信號頻率為 25 MHz,該 PFD 可檢測的最大相位誤差是多少?

解答

首先計算 τH 和 τL:

τH = 與門延遲 + 觸發器復位操作延遲 = 1.5 + 2.5 = 4 ns

τL 最小值 = 與門延遲 + 觸發器復位恢復時間 = 1.5 + 3 = 4.5 ns

因此,由非零門延遲導致 Up-Dn 為低的最小時長為:

τmin=τH+τL=4+4.5=8.5 ns

將 ωR=2π×25 MHz 和 τmin=8.5 ns 代入式 3,最大可檢測相位誤差為:

Δ?max=2π?2π×25×106×8.5×10?9≈0.79×2π rad 式 4

可見,雖然理想 PFD 可檢測的最大相位誤差為 2π 弧度,但在給定門延遲下,最大可檢測相位誤差降至 4.95 弧度,縮減為原來的 0.79 倍。

PFD 的等效狀態圖

在本系列前文中我們了解到,RS 觸發器鑒相器可建模為一個二態器件,其狀態圖如圖 5 所示。

圖 5 RS 觸發器鑒相器(左)及其等效狀態圖(右)

PFD 同樣可以用狀態機建模。粗略分析可知,PFD 等效為至少具有三個獨立狀態的狀態機:

狀態 0:Up = 0,Dn = 0

狀態 1:Up = 1,Dn = 0

狀態 2:Up = 0,Dn = 1

如圖 6 所示。

圖 6 PFD 電路的狀態圖

當 PFD 處于狀態 0(Up=0,Dn=0)時,R 輸入的上升沿會使系統切換到狀態 1(Up=1,Dn=0)。電路保持該狀態,直到 V 輸入的上升沿復位觸發器,使系統回到狀態 0。

如圖 6 所示,V 輸入的上升沿會使系統從狀態 0 切換到狀態 2(Up=0,Dn=1)。電路保持該狀態,直到 R 輸入的上升沿復位觸發器,使系統回到狀態 0(Up=0,Dn=0)。

需要注意,上述狀態圖只是系統的基礎模型。如圖 4 所示,Up 和 Dn 可能會短暫同時為高。因此,更精確的系統模型應包含第四個狀態:Up = 1 且 Dn = 1。

總結

PFD 設計的一個核心要點是防止電路各節點產生過窄脈沖。這些由快速反饋環路產生的侏儒脈沖會導致后級電路工作異常。為確保正常工作,必須在反饋通路中加入合適的延遲。但需要注意,反饋延遲會限制 PFD 的最大可檢測相位誤差以及最高工作頻率。

評論