深入理解 I2C 協(xié)議

互連集成電路(I2C)協(xié)議一直是短距離、板內(nèi)通信的核心技術(shù)。然而,實現(xiàn)穩(wěn)定可靠的 I2C 通信并非僅僅連接兩根線那么簡單。本文通過常見問題解析,深入探討開漏物理層與寄存器級尋址的技術(shù)細(xì)節(jié),幫助讀者更透徹地理解 I2C 通信原理。

I2C 與 SPI 等推挽式接口有何區(qū)別?

I2C 最核心的特征是開漏(或開集電極)架構(gòu)。

與 SPI、UART 采用推挽驅(qū)動、主動將信號線拉至高電平或低電平不同,I2C 設(shè)備只能主動將總線拉低,無法主動拉高。

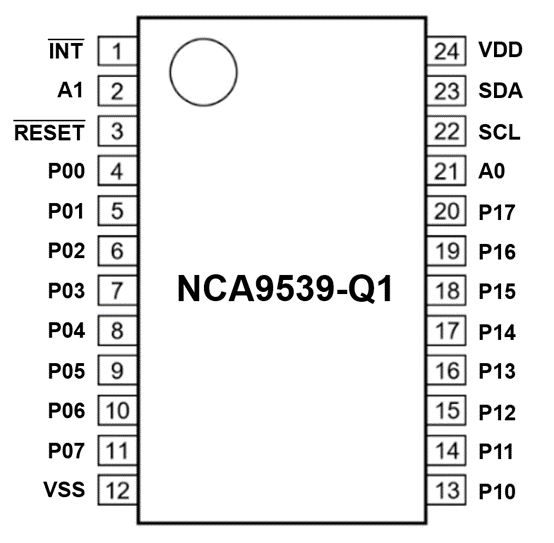

圖 1 展示了該拓?fù)浣Y(jié)構(gòu):多個設(shè)備(控制器與目標(biāo)設(shè)備)連接到共享的串行數(shù)據(jù)線(SDA)和串行時鐘線(SCL)。值得注意的是,兩條總線均通過外部上拉電阻(Rp)連接至電源電壓(VDD)。

圖 1. 簡化 I2C 系統(tǒng)拓?fù)洌故究刂破髋c多個目標(biāo)設(shè)備連接至共享 SDA、SCL 總線(圖片來源:安世半導(dǎo)體 Nexperia)

I2C 的高低電平邏輯如下:

邏輯 0(低電平):發(fā)送 0 時,器件內(nèi)部 N 溝道 MOSFET 導(dǎo)通,信號線直接接地,電路主動灌電流。

邏輯 1(高電平):發(fā)送 1 時,器件關(guān)斷內(nèi)部 MOSFET,引腳進入高阻態(tài),總線懸空,由外部上拉電阻將電壓拉回 VDD。

多主機系統(tǒng)中為何必須采用開漏架構(gòu)?

該架構(gòu)形成了線與(Wired?AND)邏輯。

由于沒有設(shè)備主動輸出高電平,多個設(shè)備可同時掛接在總線上,不會出現(xiàn)一個設(shè)備輸出高電平、另一個拉低而導(dǎo)致 VDD 到 GND 短路的風(fēng)險。

只要任意一個設(shè)備將總線拉低,整個總線就會呈現(xiàn)低電平。這一物理特性支撐了 I2C 兩項關(guān)鍵功能:

時鐘同步:低速目標(biāo)設(shè)備可拉低 SCL,暫停控制器傳輸。

總線仲裁:多控制器系統(tǒng)中,若兩個控制器同時發(fā)送,發(fā)送 0 的一方會 “覆蓋” 發(fā)送 1 的一方,實現(xiàn)非破壞性仲裁。

有效 I2C 通信的基本規(guī)則

圖 2 展示了完整的 I2C 幀結(jié)構(gòu):8 位數(shù)據(jù)、高位先行、雙向傳輸協(xié)議。為便于理解,可將通信分為三部分。

圖 2. 完整 I2C 數(shù)據(jù)傳輸結(jié)構(gòu)(圖片來源:恩智浦半導(dǎo)體 NXP)

傳輸事務(wù)

傳輸幀由僅在時鐘為高電平時才會出現(xiàn)的特定電氣狀態(tài)界定:

起始條件(S):SCL 為高電平時,SDA 從高電平變?yōu)榈碗娖健?/p>

用于喚醒總線上所有設(shè)備并開始監(jiān)聽。

停止條件(P):SCL 為高電平時,SDA 從低電平變?yōu)楦唠娖健?/p>

標(biāo)志事務(wù)結(jié)束,總線回到空閑狀態(tài)。

注意:數(shù)據(jù)傳輸期間,SCL 為高電平時 SDA 必須保持穩(wěn)定,僅允許在 SCL 低電平時改變狀態(tài)。

地址處理

起始條件后的第一個字節(jié)為地址幀,包含:

目標(biāo)地址(7 位):從機設(shè)備的唯一標(biāo)識。

讀 / 寫位(1 位):該字節(jié)最低位。

0:寫操作(控制器 → 目標(biāo)設(shè)備)

1:讀操作(目標(biāo)設(shè)備 → 控制器)

第 9 位:應(yīng)答位

每傳輸一個字節(jié)(地址或數(shù)據(jù))后,都會跟隨第 9 個時鐘脈沖,即應(yīng)答位(ACK/NACK)。

ACK(邏輯 0):接收方拉低 SDA,表示已正確接收該字節(jié)。

NACK(邏輯 1):接收方保持 SDA 高電平,表示非應(yīng)答。

通常代表設(shè)備不存在、設(shè)備忙或讀序列結(jié)束。

實例分析

以下是 I2C 在硬件層面寫入設(shè)備內(nèi)部指定寄存器的實際應(yīng)用。圖 3 展示對德州儀器 DAC80501 數(shù)模轉(zhuǎn)換器進行多字節(jié)寫入的過程。

圖 3. I2C 寫幀解析,展示配置外設(shè)所需的地址、命令與數(shù)據(jù)字節(jié)序列(圖片來源:德州儀器 Texas Instruments)

操作可簡化為三步:

地址幀:控制器發(fā)送地址 + 寫位(如 0x49 + 0)。

命令幀:控制器發(fā)送寄存器指針(如 0x08),

告知 DAC 后續(xù)數(shù)據(jù)將寫入 DAC 數(shù)據(jù)寄存器。

數(shù)據(jù)幀:控制器發(fā)送 16 位電壓值(高位在前,低位在后)。

這是執(zhí)行器類設(shè)備的標(biāo)準(zhǔn)工作流程:地址 → 命令 → 數(shù)據(jù)。

總結(jié)

掌握 I2C 不能只停留在調(diào)用庫函數(shù)層面,還需要理解:

高電平是被動上拉而非主動驅(qū)動;

第 9 位(ACK)是有效數(shù)據(jù)傳輸?shù)?strong>基礎(chǔ)握手機制;

復(fù)雜的寄存器訪問幾乎都遵循先寫指針,再發(fā)起重復(fù)起始條件的流程。

評論