基于大規(guī)模并行GPU光柵化器加速計算光刻技術(shù)

隨著半導(dǎo)體制造工藝不斷向更先進的納米制程邁進,計算光刻已從芯片設(shè)計的輔助環(huán)節(jié),發(fā)展成為先進芯片設(shè)計的核心支柱。如今,掩模合成、光刻仿真以及光學(xué)鄰近效應(yīng)校正(OPC)對計算精度和數(shù)據(jù)處理吞吐量提出了前所未有的要求。而這些工作流程的核心環(huán)節(jié)便是光柵化—— 將復(fù)雜的幾何版圖轉(zhuǎn)換為超高分辨率像素網(wǎng)格的過程。

西門子EDA部門近期發(fā)布了一份白皮書,提出了應(yīng)對該問題的創(chuàng)新方案。書中深入剖析了光柵化成為技術(shù)瓶頸的原因,以及基于大規(guī)模并行 GPU 架構(gòu)的創(chuàng)新光柵化算法如何破解相關(guān)難題,并通過實際性能測試結(jié)果,展現(xiàn)了這一創(chuàng)新技術(shù)對下一代半導(dǎo)體制造的重要影響。

光刻領(lǐng)域中光柵化的重要性空前提升

光柵化常被與計算機圖形學(xué)關(guān)聯(lián),但在電子設(shè)計自動化(EDA)領(lǐng)域,它的作用遠為關(guān)鍵。在計算光刻中,光柵化后的版圖被用于模擬光線透過掩模的傳播路徑,以及光刻膠在納米尺度下的反應(yīng)效果。與圖形學(xué)應(yīng)用中僅將像素簡單判定為

“開啟” 或 “關(guān)閉”

不同,光刻領(lǐng)域要求精準(zhǔn)的像素部分覆蓋率計算,且需嚴格保留超精細圖形之間的連接性。光柵化過程中產(chǎn)生的微小誤差,會在仿真和光學(xué)鄰近效應(yīng)校正的循環(huán)過程中不斷放大,最終影響芯片的良率和可制造性。

隨著半導(dǎo)體工藝節(jié)點向數(shù)納米以下演進,光柵化所需的分辨率呈爆炸式增長,且在迭代式光學(xué)鄰近效應(yīng)校正流程中,相同的光柵化操作需要重復(fù)執(zhí)行多次。即便是經(jīng)過高度優(yōu)化的基于 CPU 的光柵化器,也難以滿足算力需求,光柵化因此成為制約整體運行效率的主要瓶頸。

傳統(tǒng)光柵化方法的局限性

多數(shù)傳統(tǒng)光柵化技術(shù)采用二進制覆蓋模型,該模型在圖形可視化場景中表現(xiàn)良好,但在光刻領(lǐng)域則難以適用。這類方法無法捕捉細微的光強變化,在處理細線條或緊密排布的圖形時,還極易產(chǎn)生連接性失真問題。同時,現(xiàn)代芯片版圖包含數(shù)十億個多邊形,像素評估次數(shù)更是高達萬億級,其龐大的數(shù)據(jù)規(guī)模對內(nèi)存帶寬和計算資源造成了巨大壓力。

正是在這一背景下,GPU 的優(yōu)勢開始凸顯。GPU 的大規(guī)模并行處理能力非常適配數(shù)據(jù)密集型工作負載,但同時也帶來了不規(guī)則內(nèi)存訪問模式、對數(shù)值精度高度敏感等挑戰(zhàn)。要將 GPU 成功應(yīng)用于光刻光柵化,必須設(shè)計出以精度優(yōu)先為核心、適配大規(guī)模并行執(zhí)行的專屬算法。

為 GPU 重構(gòu)光柵化技術(shù)邏輯

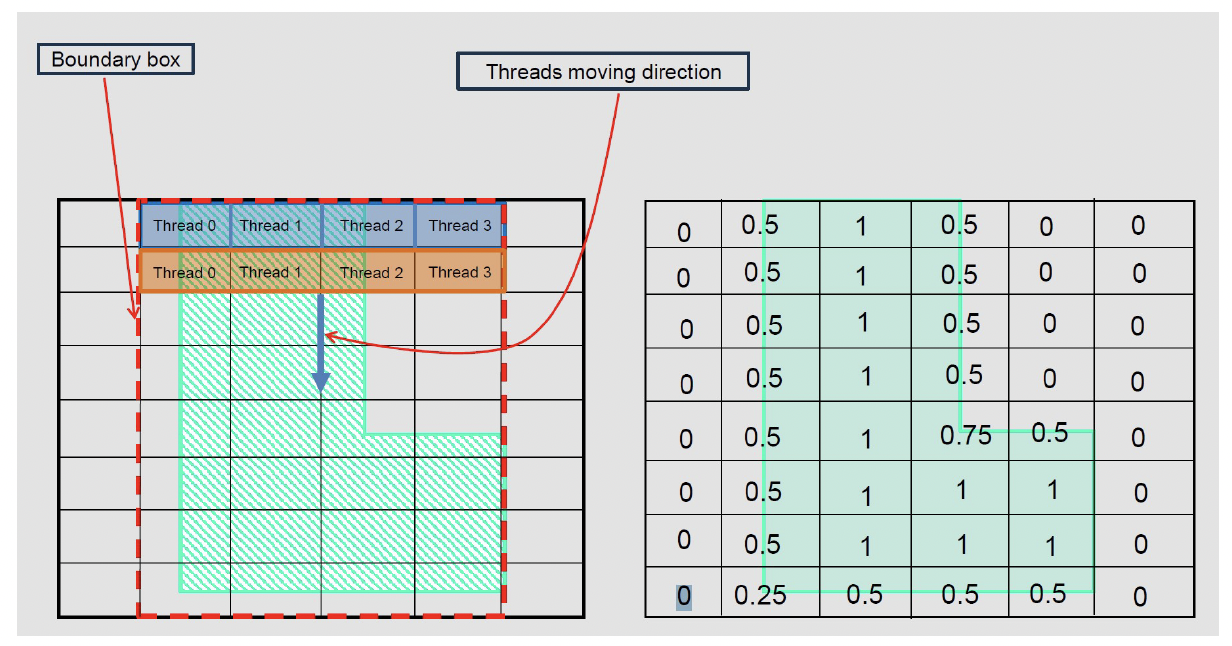

面向計算光刻的 GPU 優(yōu)化光柵化器,從設(shè)計理念上便與傳統(tǒng)方案截然不同。該技術(shù)不再對多邊形進行串行處理,而是將版圖按空間維度分解為多個可并行光柵化的獨立區(qū)域,每個區(qū)域?qū)?yīng)映射至 GPU 的線程塊,使數(shù)千個線程能夠同時執(zhí)行像素覆蓋率評估。

像素覆蓋率的計算采用浮點運算而非近似算法,確保邊界相互作用的計算精度達到納米級別。技術(shù)研發(fā)中還特別注重保留亞像素級的連接性,避免細線條圖形在光柵化過程中發(fā)生非預(yù)期的斷裂。對于曼哈頓幾何圖形,技術(shù)通過簡化評估流程提升效率;對于曲線圖形,則采用兼具通用性和并行友好性的處理方法。

GPU 光柵化流水線的工作原理

GPU

光柵化流水線的處理始于 CPU 端的預(yù)處理階段:先對版圖數(shù)據(jù)進行解析,并按空間分塊歸類,再將這些數(shù)據(jù)塊以優(yōu)化的內(nèi)存布局傳輸至

GPU,實現(xiàn)合并式內(nèi)存訪問。在 GPU

端,各數(shù)據(jù)塊被獨立處理:幾何數(shù)據(jù)被緩存至共享內(nèi)存,線程被分配至單個像素或小型像素組,每個線程獨立計算其負責(zé)的像素處于多邊形內(nèi)部、外部還是邊界位置。

處于邊界的像素會得到特殊處理:通過解析算法計算與像素相交的多邊形邊緣,精準(zhǔn)求解像素被多邊形覆蓋的面積比例。當(dāng)多個多邊形作用于同一像素時,通過原子操作實現(xiàn)覆蓋率的準(zhǔn)確累加。這一設(shè)計方案同時實現(xiàn)了高性能和確定性精度

—— 這兩大特性在大規(guī)模并行系統(tǒng)中通常難以兼得。

該技術(shù)基于 CUDA 編程模型開發(fā),在英偉達新一代數(shù)據(jù)中心 GPU 上運行時表現(xiàn)尤為優(yōu)異,這類 GPU 能為超高分辨率光柵化提供所需的內(nèi)存帶寬和并發(fā)處理能力。

基于英偉達 H100 GPU 的實際性能測試結(jié)果

性能基準(zhǔn)測試得出了極具說服力的結(jié)論:與高度優(yōu)化的

CPU 光柵化器相比,基于 GPU 的光柵化方案在各類版圖處理中均實現(xiàn)了性能的大幅提升。針對以曼哈頓幾何圖形為主的芯片設(shè)計,性能提升最高達

290 倍;即便是處理難度更高的曲線版圖,GPU 光柵化器也實現(xiàn)了最高 45 倍的性能提升。

至關(guān)重要的是,性能的提升并未以犧牲精度為代價。在所有測試場景中,該方案的計算絕對誤差相較于 CPU 基準(zhǔn)計算結(jié)果均低于 1%。這一精度水平滿足了計算光刻領(lǐng)域的嚴苛要求,也印證了大規(guī)模并行處理與納米級計算精度能夠?qū)崿F(xiàn)兼容。

對電子設(shè)計自動化與半導(dǎo)體制造領(lǐng)域的重要意義

GPU

加速光柵化技術(shù)的價值,遠不止體現(xiàn)在單純的性能指標(biāo)提升上。更快的光柵化處理速度能夠縮短光學(xué)鄰近效應(yīng)校正和掩模合成的周期,讓工程師在相同的設(shè)計窗口期內(nèi)完成更多次迭代優(yōu)化,進而提升校正質(zhì)量、提高芯片良率、縮短產(chǎn)品上市周期。而高精度的計算能力和圖形連接性保留能力,確保了性能提升不會為制造流程引入新的風(fēng)險。

隨著芯片設(shè)計中復(fù)雜的非曼哈頓幾何圖形越來越多,且光刻仿真的保真度要求持續(xù)提高,基于 GPU 的光柵化技術(shù)的可擴展性展現(xiàn)出更高的價值。這一曾經(jīng)的技術(shù)瓶頸,如今已成為光刻流水線中具備可擴展性、面向未來的核心組件。

總結(jié)

基于大規(guī)模并行

GPU 的光柵化技術(shù),標(biāo)志著計算光刻工作負載處理方式的重大變革。隨著 GPU

架構(gòu)的持續(xù)演進,核心數(shù)量不斷增加、內(nèi)存帶寬持續(xù)提升,該技術(shù)的性能優(yōu)勢將進一步擴大。未來的研發(fā)工作將聚焦于三大方向:與現(xiàn)有電子設(shè)計自動化平臺的深度集成、對

CPU-GPU 異構(gòu)工作流程的支持,以及向更先進光刻模型和三維效應(yīng)仿真場景的技術(shù)拓展。

評論