小梅哥和你一起深入學習FPGA之數碼鐘(上)

一、 實驗目的

本文引用地址:http://www.cqxgywz.com/article/274342.htm實現數碼時鐘的功能,要求能夠進行24時制時、分、秒的顯示,并能夠通過按鍵調整時間。

二、 實驗原理

通過對系統時鐘進行計數,獲得1S的標準信號,再以該信號為基礎,進行時、分、秒的計數,通過數碼管將該計數值顯示出來,即可實現數字鐘的功能。同時可以使用獨立按鍵對時、分、秒計數器的初始值進行設置,即可實現時間的設定。

三、 硬件設計

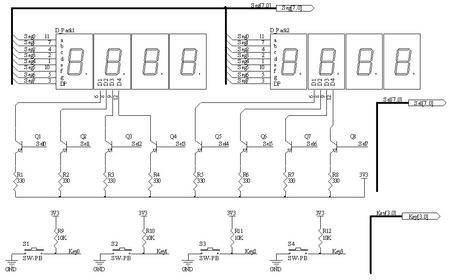

本實驗硬件電路簡單,用到了8個數碼管和4個獨立按鍵。硬件電路如下:

圖3-1 數字鐘電路

四、 架構設計

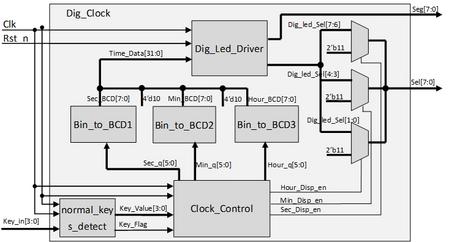

本實驗設計架構模塊較多,下圖為數字鐘的架構:

圖4-1 數字鐘實驗模塊組織結構圖

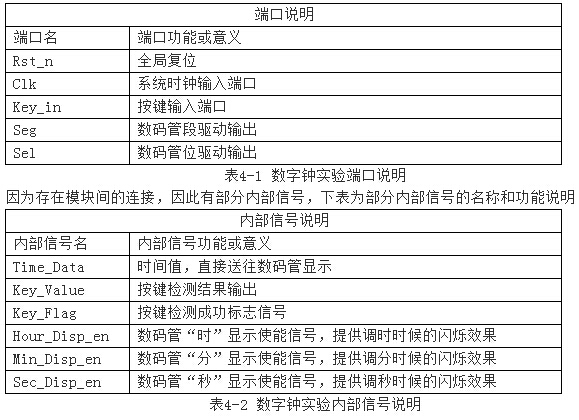

由圖可知本實驗有16個輸出端口和6個輸入端口,各端口的意義如下

fpga相關文章:fpga是什么

評論