碳化硅賦能浪潮教程:利用 SiC CJFET替代超結 MOSFET

- 2026-03-27碳化硅賦能浪潮教程:SiC JFET驅動工業與服務器電源革新

- 2026-04-14碳化硅賦能浪潮教程:替代Si 和SiC MOSFET的方案

- 2026-04-22碳化硅賦能浪潮教程:利用 SiC CJFET替代超結 MOSFET

碳化硅(SiC)憑借其優異的材料特性,在服務器、工業電源等關鍵領域掀起技術變革浪潮。本教程聚焦 SiC 尤其是 SiC JFET 系列器件,從碳化硅如何重構電源設計邏輯出發,剖析其在工業與服務器電源場景的應用價值。

我們已經介紹了

碳化硅如何革新電源設計、工業與服務器電源。

三種替代 Si 和 SiC MOSFET的方案。

SiC Cascode JFET的動態特性、SiC Combo JFET的應用靈活性。

本文將介紹利用 SiC CJFET替代超結 MOSFET以及開關電源應用。

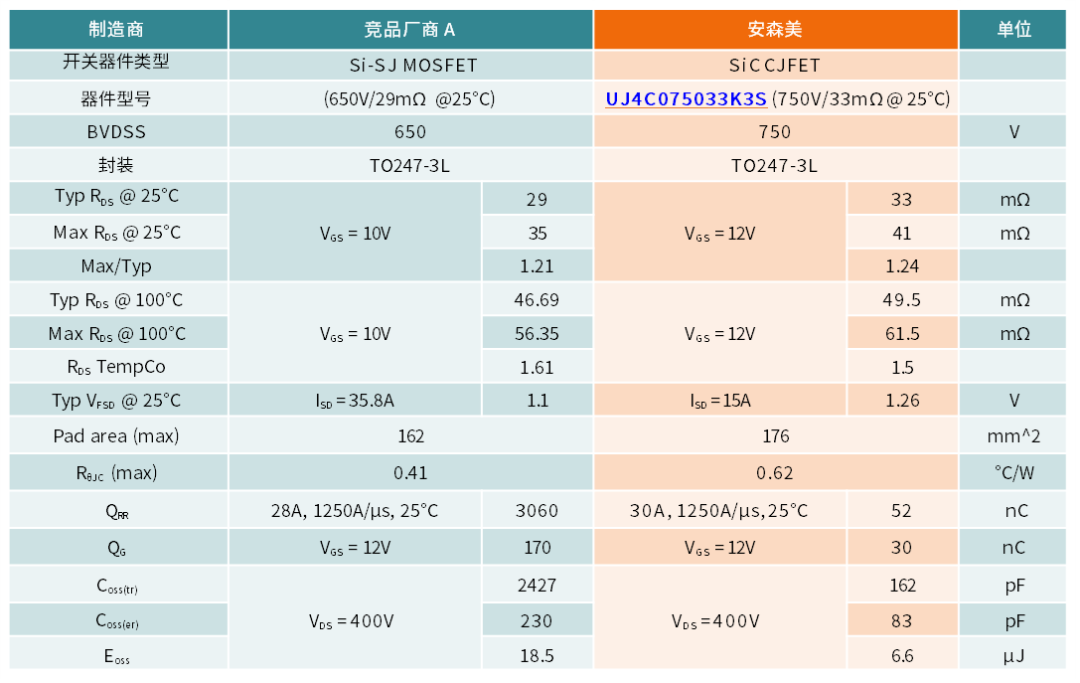

安森美與競品對比

本表對比了安森美(onsemi) EliteSiC CJFET 器件 UJ4C075033K3S 與某競品廠商的Si超結(SJ) MOSFET 的關鍵特性。其中,UJ4C075033K3S 在25°C 下的額定值為 750 V,33 mΩ; 而競品Si SJ MOSFET 在25°C 下的額定值為 650 V,29 mΩ。在此對比中,該 CJFET 的反向恢復電荷 QRR 降低至 1/60,柵極電荷 QG 降低至 1/6,反向傳輸電容 COSS(tr) 降低至 1/10。

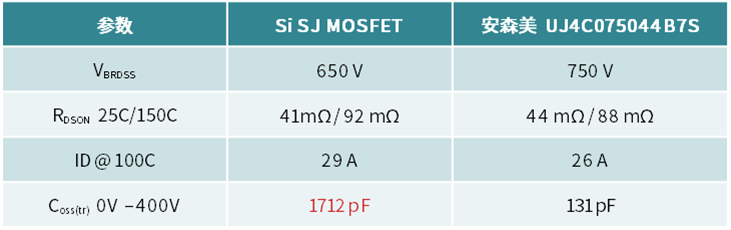

最大限度降低反向傳輸電容

SiC CJFET 與 Si SJ MOSFET 之間最顯著的差異在于電容特性與裸片尺寸。在安森美 UJ4C075044B7S CJFET 與某競品 Si SJ MOSFET 的對比中,盡管 CJFET 的阻斷電壓 VBRDSS 高出 100V,且兩者的導通電阻 RDS(on) 額定值相近,但 SJ MOSFET 的反向傳輸電容 COSS(tr) 卻高出 13倍 以上。這一差異源于 SJ MOSFET在低壓范圍內表現出的非線性特性,如下圖所示。CJFET 的電壓轉換時間遠短于SJ MOSFET 。在采用半橋整流拓撲(而非全橋)的電源系統中,CJFET 能始終實現顯著更快的開關速度。

降低導通損耗,縮短死區時間

在用 SiC CJFET替代 Si SJ MOSFET 時,安森美建議通過調整死區時間(dead time)或在 CJFET 上增加緩沖電容,以有效管理因死區引起的導通損耗。尤其在較高開關頻率下,死區時間帶來的影響會變得更加顯著。

對于CJFET而言,從檢測到電流反向到JFET溝道完全導通通常存在延遲。舉例來說:若死區時間為 100 ns,而開關頻率為 100 kHz,則開關周期為 10 μs,此時死區僅占周期的 1%,該延遲影響相對較小。然而,若開關頻率提升至 1 MHz,開關周期將縮短至 1 μs,死區時間便占整個周期的 10%,其影響不可忽視。

在相同死區時間下,相較于 Si SJ MOSFET,SiC CJFET 的漏源電壓 VDS 放電速度更快,導致其體二極管在剩余死區時間內持續導通。假設 CJFET 剩余死區時間 TDT(CJFET) 為 0.2 μs,體二極管正向壓降 VFD 為 1.2 V,開關頻率 FSW 為 100 kHz,開關電流 IC 為 10 A,則全橋拓撲中由剩余死區引起的功率損耗 PDT 可通過以下公式計算:

在此案例中,計算得出的損耗為0.96W。然而,通過對柵極應用Adaptive Gate Control, 在死區時間內提前提升 VG2,讓 VDS(CJFET) 降至 0V 的瞬間開通。即可使該部分損耗趨近于零。這一效果可通過觀測 VDS 與 VGS 的輸出波形加以驗證。

死區時間越長,體二極管導通損耗的持續時間也越長。通過縮短 CJFET 的死區時間,或為其增加緩沖電容以匹配 Si SJ MOSFET 的 COSS ,可有效改善此問題。

消除反向恢復失效風險

在對比 SiC CJFET與Si SJ MOSFET時,當兩者具有相同的電流變化率( Δi/Δt )并在相同的結溫( TJ = 25°C )下工作,安森美UJ4C075033K3S CJFET 的反向恢復電荷( QRR )最多可比后者低 60 倍 。更小的反向恢復電荷意味著更高效率、更低噪聲與更優的電磁兼容性。此外,CJFET在反向恢復過程中沒有導致器件失效的風險,可顯著提升系統整體穩健性。

2、開關電源應用

適用于任何電壓等級的高能效表現

為展示CJFET在電源快速開關需求下的性能,我們測試了四款不同的安森美 CJFET 器件在3.6 kW圖騰柱功率因數校正 (TPPFC) 硬開關拓撲中的效率。所有被測CJFET在半負載條件下均實現了超過99% 的峰值效率。

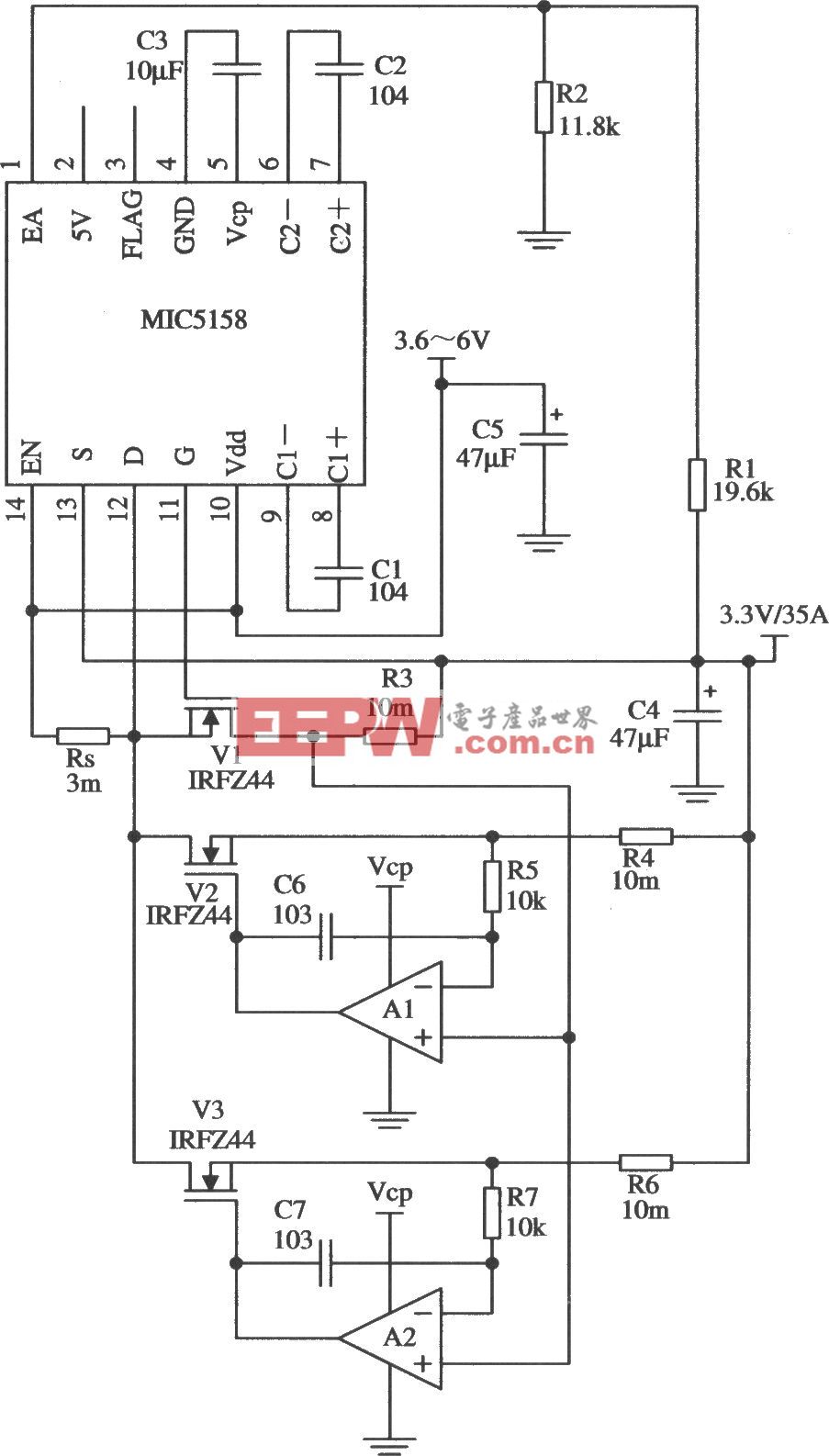

同步整流 (SR) 技術

同步整流的實現,首先在于用可控的場效應晶體管(FET)替代諧振型電源轉換器中通常在初級側(有時也在次級側)使用的二極管。由于這些 FET 的開關時序可以更直接地控制,轉換器輸出的直流波形能夠更準確地匹配負載所需的電壓和頻率。

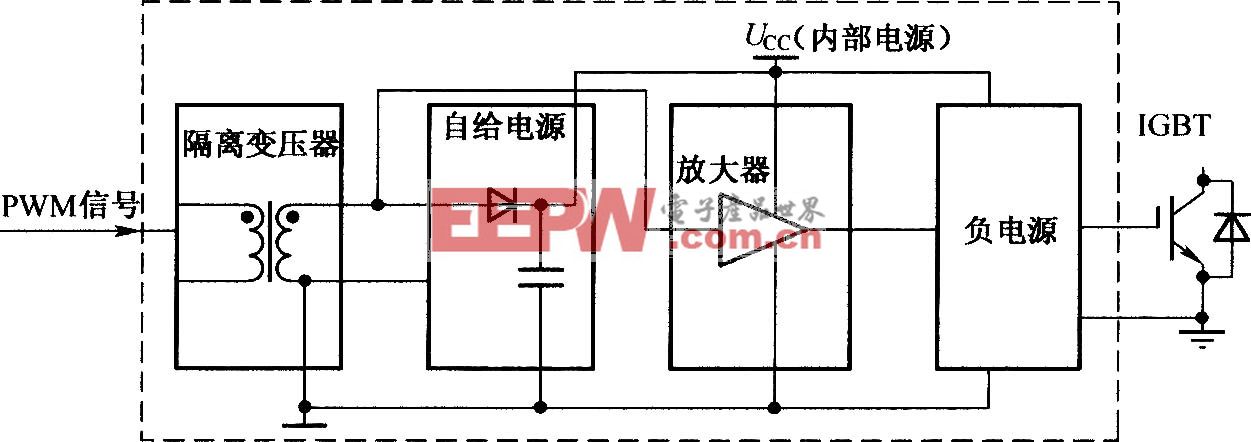

全橋移相有源橋零電壓轉換拓撲

以這種在 AC-DC 應用中日益普及的電路拓撲為例:所有通常使用二極管的開關位置均被場效應晶體管替代。“ZVT”代表零電壓轉換,該技術巧妙利用了主變壓器的漏電感與開關的輸出電容——這些通常被視為寄生元件的特性——并將其轉化為優勢。

例如,在標準全橋拓撲中置于初級側外部的漏電感,現在可集成至內部。它在實現相同功能的同時,大幅縮減了占用空間。

通過有源橋移相控制,脈寬調制(PWM)可轉換為固定開關頻率的工作模式,這使控制實現更為簡便,同時降低了開關對擊穿電壓的耐壓要求。電磁干擾頻譜也更為集中,使系統在整個寬輸出電壓范圍內均能實現穩定且高效率的運行。

零電壓開關(ZVS)

從電氣工程師的角度來看,全橋功率轉換過程的一大優勢在于它能夠實現軟開關。嚴格來說,ZVS 并非一種刻意設計的技術手段,而更像是一種可被巧妙利用的物理現象。它通過功率轉換器的諧振網絡(或稱“諧振腔”)得以實現。

典型的零電壓開關會利用電容和電感構成一個諧振電路(即“諧振腔”)。而在實際應用中,常以變壓器固有的勵磁電流作為便捷的替代。可以把這個勵磁電流看作一種振蕩信號,它能夠在PFC電路中 MOSFET(或 CJFET)兩端電壓為零(或極低)時,將器件導通。

波形整形的核心思想是:在輸入電壓處于波峰或波谷時導通或關斷輸出開關,而諧振所產生的自然振蕩,恰好為這種基于電感特性的開關動作提供了理想時序。

該電流被有意設置為相位滯后于諧振網絡的電壓,正是這種滯后引發了諧振,從而觸發場效應晶體管導通(并促使其他開關按序關斷)。在此過程中,開關損耗得以有效避免,EMI 噪聲也顯著降低。

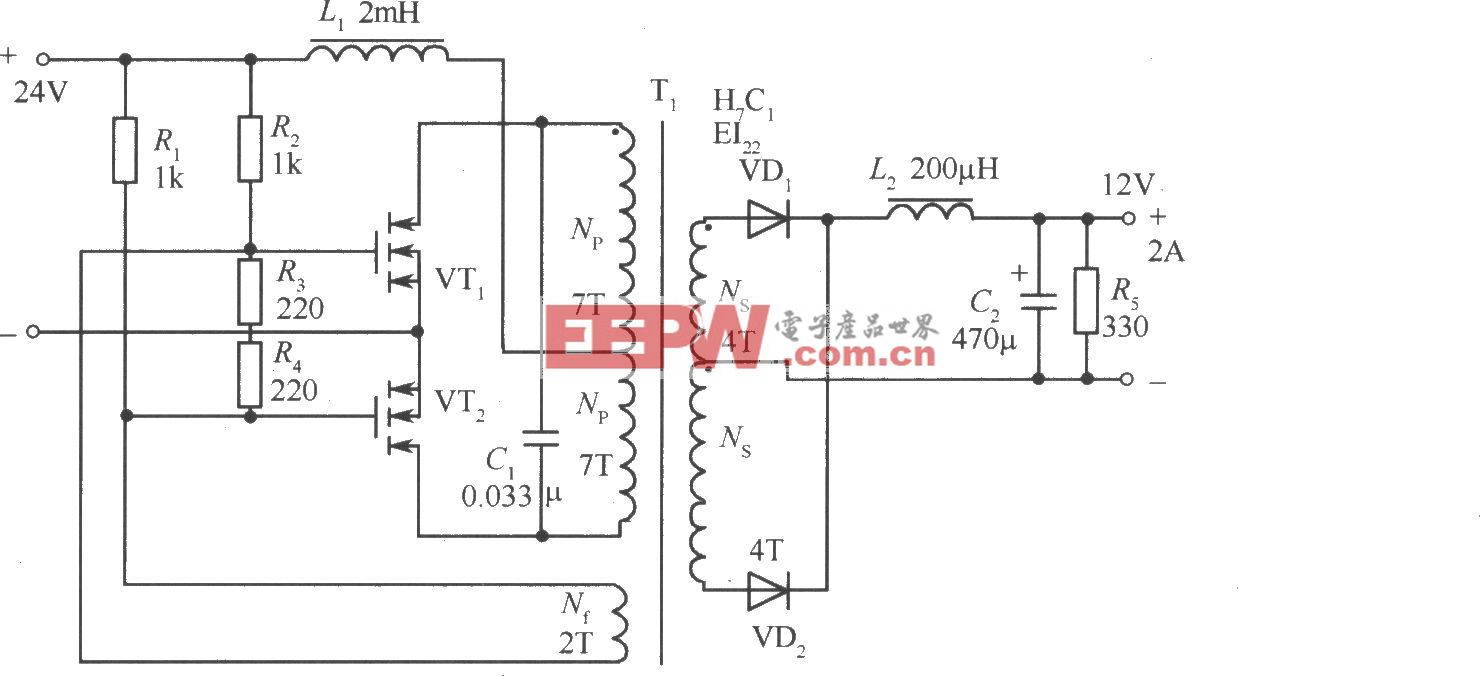

高頻電源的五個轉換級

這是前文介紹的圖騰柱PFC完整電路圖。這種全"無橋式"拓撲結構包含五個功率轉換級。最左側為硬開關,其余四個均采用軟開關技術。從左至右,每個同步整流轉換級的電路結構逐級簡化。

對于“快速橋臂”(即硬開關),圖騰柱PFC需搭配RC緩沖器使用CJFET。若PCB布局空間受限無法容納此元件,則 SiC MOSFET 可能成為唯一選擇。否則,若考慮 CJFET 配合 RC 緩沖電路所能實現的性能特性,CJFET 將是更優方案。

對于"慢速橋臂"(即同步整流器件),其核心要求是具備低導通電阻RDS(on) ,因此CJFET是最佳選擇。

對于位于中間的初級 LLC 轉換級(因其緊鄰兩個電感L和一個電容C而得名),導通損耗是主要損耗因素。在高開關頻率下,關斷開關損耗是另一個關鍵參數,因為 LLC 作為一種零電壓開關(ZVS)拓撲,不存在導通損耗。CJFET 在配置緩沖器后已展現出極低的關斷能量損耗Eoff ,因此是初級 LLC 轉換級的最佳選擇。

隨后的次級 LLC 轉換級以及最右側的 O-Ring 級可用于 400 V 輸出電壓的設計中。對于此類高壓應用,低導通電阻 RDS(on) 和低輸出電容 COSS 至關重要,這使得 CJFET 在整個次級側相比 SiC MOSFET 或 Si SJ MOSFET 更具優勢。

未完待續,我們將介紹CJFET通常需要配置緩沖電路的原因等。

評論