內(nèi)存墻越筑越高

隨著靜態(tài)隨機存取存儲器(SRAM)在先進(jìn)工藝節(jié)點下難以持續(xù)微縮,整個半導(dǎo)體行業(yè)必須評估其對各類計算場景的沖擊,而短期內(nèi)暫無簡易解決方案。

核心要點

每一代工藝節(jié)點微縮時,同等容量的 SRAM 所占芯片面積比例持續(xù)上升。

該問題不僅局限于前沿 AI 芯片,最終將影響所有計算設(shè)備,甚至小型微控制器(MCU)與微處理器(MPU)。

行業(yè)可能需要進(jìn)行架構(gòu)變革;在邏輯芯片上堆疊 SRAM 小芯片可行,但成本高昂。

SRAM 是所有計算系統(tǒng)的核心組件,但其縮放進(jìn)度已無法跟上邏輯電路的迭代速度,過去五年這一矛盾急劇惡化。

早在 1990 年,亨尼西與帕特森在《計算機架構(gòu):量化方法》一書中就明確指出:無論從容量還是性能來看,內(nèi)存都將成為未來處理器發(fā)展的核心障礙。數(shù)十年來,硬件架構(gòu)一直圍繞這一難題優(yōu)化,通常以 SRAM 作為高速緩存,搭配片外更大容量的動態(tài)隨機存取存儲器(DRAM)。這種方案讓內(nèi)存看起來更大,但速度往往慢得多,這就是著名的內(nèi)存墻。

在所有計算場景中,程序與數(shù)據(jù)都存儲在 SRAM 里,處理器從該內(nèi)存讀取指令,指令再指示處理器對同樣存儲于此的數(shù)據(jù)執(zhí)行操作。

SRAM 比處理器內(nèi)部暫存數(shù)據(jù)的寄存器更經(jīng)濟(jì)。盡管寄存器單元與 SRAM 使用的晶體管數(shù)量相當(dāng),但寄存器的解碼與訪問機制更昂貴,無法隨寄存器組規(guī)模同步縮放。

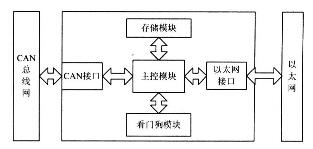

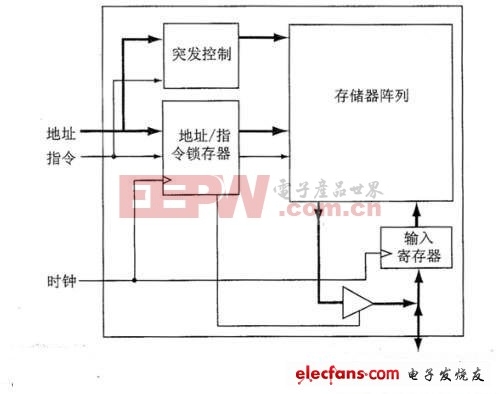

SRAM 由存儲單元陣列與外圍電路組成,支持?jǐn)?shù)據(jù)隨機讀寫。多數(shù)情況下,外圍電路為半定制設(shè)計,會隨內(nèi)存陣列擴(kuò)大而調(diào)整。事實上,內(nèi)存速度的提升很多來自外圍電路優(yōu)化,而非存儲陣列本身。

SRAM 的容量與性能提升已近乎停滯,前景愈發(fā)嚴(yán)峻。這意味著:每一代工藝節(jié)點微縮,同等容量 SRAM 占用的芯片面積占比不斷攀升。當(dāng)更多芯片達(dá)到掩模版極限時,無法承受這種面積開銷,不得不更多依賴外部內(nèi)存,而外部內(nèi)存速度要慢數(shù)個數(shù)量級。

在 AI 時代,內(nèi)存訪問模式發(fā)生改變,內(nèi)存墻迅速成為主要性能瓶頸。

臺積電承認(rèn) SRAM 縮放存在問題,但該代工廠聲稱其全新 2 納米納米片技術(shù)已實現(xiàn)改進(jìn)。不過,目前缺乏確鑿數(shù)據(jù)支撐。以往經(jīng)驗顯示,大規(guī)模商用前公布的指標(biāo),實際表現(xiàn)往往打折扣。

SRAM 縮放停滯

從邏輯上看,晶體管尺寸縮小,由 6 個晶體管構(gòu)成的 SRAM 單元尺寸與性能也應(yīng)同步提升。

新思科技嵌入式內(nèi)存 IP 首席產(chǎn)品經(jīng)理達(dá)里爾?塞策表示:SRAM 縮放停滯,源于經(jīng)典 6T 位單元觸及物理極限與工藝離散性限制。SRAM 位單元設(shè)計初衷是追求高密度,但存在讀寫需求沖突的固有缺陷:訪問晶體管與存儲晶體管相互制約,二者必須精細(xì)平衡并兼容工藝偏差。當(dāng)幾何尺寸持續(xù)縮小,偏差對位單元讀寫特性的影響占比顯著放大。

問題不止于此。

Arteris 產(chǎn)品管理高級經(jīng)理安德烈?博納爾多指出:工藝節(jié)點微縮時,靜電控制與隨機離散性成為主導(dǎo)約束,阻止單元面積按比例縮小。此外,SRAM 速度已進(jìn)入平臺期,因為連線電阻與位線電容上升,而近期工藝節(jié)點的核心電壓(Vdd)幾乎未降低。邏輯電路可通過器件與布線創(chuàng)新持續(xù)縮放,但 SRAM 做不到。

在 2 納米及更先進(jìn)工藝上,SRAM 位單元縮放帶來的密度提升已不足 15%,遠(yuǎn)低于 65 納米到 5 納米時代每代 50%–100% 的大幅微縮。這種下滑源于先進(jìn)節(jié)點下器件、柵極接觸、中層互連(MEOL)、V0/V1 線寬極窄,進(jìn)一步有效縮放受限于設(shè)備與良率。

其直接后果是成本更高、性能更差。

Quadric 首席技術(shù)官奈杰爾?德雷戈表示:主要表現(xiàn)為內(nèi)存密度縮放落后于邏輯電路,每平方毫米門數(shù)增長快于每平方毫米兆字節(jié)數(shù)。同時,線路延遲與物理定律導(dǎo)致訪問速度下滑,不過智能架構(gòu)調(diào)整可緩解邏輯電路與 SRAM 速度的依賴關(guān)系。

自上世紀(jì) 80 年代以來,內(nèi)存與計算的差距持續(xù)擴(kuò)大。如今計算機性能提升了近五個數(shù)量級,但內(nèi)存帶寬提升甚至不到 100 倍,處理器可處理的數(shù)據(jù)量與實際能獲取的數(shù)據(jù)量之間存在超過 1000 倍的差距。

這不僅是前沿 AI 技術(shù)的問題,最終將影響所有設(shè)備,甚至小型 MCU 與 MPU,尤其隨著 AI 向邊緣滲透。

瑞薩電子首席產(chǎn)品營銷經(jīng)理卡維塔?查爾提到:當(dāng) SRAM 無法縮放,會占據(jù)更大的芯片面積比例,這必須納入設(shè)計考量。同時影響芯片用戶,他們需要權(quán)衡片內(nèi)可實現(xiàn)功能與何時切換到外部內(nèi)存,工藝越先進(jìn),成本越高。

關(guān)于 2 納米節(jié)點的 SRAM 單元面積是否更優(yōu),行業(yè)尚無定論。

新思科技嵌入式內(nèi)存 IP 高級產(chǎn)品經(jīng)理拉胡爾?圖克拉爾表示:近期 SRAM 的收益來自將邏輯微縮技術(shù)應(yīng)用于 SRAM 宏的解碼與控制電路,即便位單元未縮放,仍能通過設(shè)計創(chuàng)新實現(xiàn)面積優(yōu)勢。未來隨著環(huán)繞柵極(GAA)技術(shù)成熟、器件寬度控制更靈活,有望進(jìn)一步改善。GAA 晶體管靜電控制更好,可降低漏電流、優(yōu)化讀寫性能。2 納米初期的內(nèi)存面積提升,主要來自解碼與數(shù)據(jù)通路電路中的邏輯器件優(yōu)化;后續(xù)節(jié)點有望通過 GAA 晶體管實現(xiàn)位單元面積進(jìn)一步縮小。

Arteris 的博納爾多總結(jié):SRAM 縮放放緩標(biāo)志著系統(tǒng)架構(gòu)進(jìn)入拐點。當(dāng)內(nèi)存密度增長減速,單純增加緩存容量在經(jīng)濟(jì)上不再高效。

對軟件的影響

內(nèi)存墻對軟件的影響廣泛,挑戰(zhàn)了 “軟件生產(chǎn)力是首要優(yōu)化目標(biāo)” 的長期理念。

依賴大量本地 SRAM 與多層高速緩存的處理器架構(gòu)受沖擊最大。通用 CPU 無法避開這種重硬件內(nèi)存架構(gòu),因為手機、筆記本、數(shù)據(jù)中心的 CPU 需要運行隨機用戶代碼,處理非結(jié)構(gòu)化內(nèi)存訪問,同時調(diào)度數(shù)十個線程。

如今 SRAM 占據(jù)更大芯片面積與成本,大型寄存器文件與緩存層級不再免費縮放,給芯片面積、良率、能效與數(shù)據(jù)搬運效率帶來壓力。瓶頸從計算密度轉(zhuǎn)向內(nèi)存架構(gòu)與互連效率。軟件必須假設(shè)內(nèi)存具有更強層級性、速度更不均勻,數(shù)據(jù)局部性、分塊、分區(qū)、流量可預(yù)測性變得更重要,延遲波動成為系統(tǒng)級性能瓶頸。

AI 同樣無法幸免。

隨著 AI 模型規(guī)模與上下文長度增長,內(nèi)存帶寬與片上緩存成為性能主導(dǎo)因素,大語言模型推理中的 KV 緩存帶寬瓶頸尤為明顯。因此,軟件必須優(yōu)化數(shù)據(jù)局部性、內(nèi)存感知調(diào)度、量化、稀疏性與內(nèi)存分層,因為計算性能提升已無法彌補內(nèi)存縮放緩慢的短板。

AI 架構(gòu)存在可利用的差異:AI 引擎(尤其是推理處理器)可長時間處理結(jié)構(gòu)化代碼,遠(yuǎn)長于任務(wù)切換的 CPU。智能 AI 架構(gòu)將內(nèi)存管理交給離線編譯器,由代碼顯式調(diào)度直接內(nèi)存訪問(DMA)傳輸模型權(quán)重與激活值,甚至可打造完全無需數(shù)據(jù)緩存的 AI 推理引擎,緩解對高速、高功耗 SRAM 的依賴。隨著更多負(fù)載基于 AI 模型,先進(jìn) SoC 可在更大面積上避開 SRAM 密度與速度瓶頸,僅在關(guān)鍵 CPU 子模塊保留該設(shè)計挑戰(zhàn)。

近期 AI 模型的算術(shù)強度(處理器在內(nèi)存數(shù)據(jù)上執(zhí)行的運算量)持續(xù)下降,導(dǎo)致對內(nèi)存到處理器的帶寬需求更高。

3D SRAM 方案

若 SRAM 無法縮放,用最昂貴工藝制造它便失去意義。行業(yè)越來越傾向于將 SRAM 做成小芯片,堆疊在處理器上方。

SoC 設(shè)計師正在探索解耦方案:在先進(jìn)工藝裸片上放置少量 SRAM,滿足 CPU/GPU/AI 對 L1、L2 甚至 L3 緩存的核心需求;更大容量的 SRAM(如 L4)則放在上一代工藝裸片上,以獲得更低的單晶體管成本。更快的裸片間互連與更精細(xì)的間距,讓多層內(nèi)存集成更簡單,成本更低且延遲可接受。

但該方案目前成本高昂。

3D 與基于小芯片的 SRAM,因封裝成本高、熱設(shè)計復(fù)雜、標(biāo)準(zhǔn)化程度有限,目前僅在高端 AI / 高性能計算(HPC)芯片上具備經(jīng)濟(jì)性。面向低成本大眾市場的 SRAM 小芯片,短期很難實現(xiàn)。

小芯片方案能以更低功耗提供數(shù)量級更高的帶寬,是破除性能墻的關(guān)鍵,不僅是 2.5D,更是 3D 集成。

替代方案

每當(dāng)內(nèi)存出現(xiàn)問題,總會出現(xiàn)替代 SRAM 的新技術(shù)討論。

新興內(nèi)存技術(shù)可在特定場景發(fā)揮作用,但無法全面替代 SRAM,未來多數(shù)系統(tǒng)將使用更多層級的內(nèi)存,而非更少。

未來系統(tǒng)架構(gòu)可能徹底改變。

內(nèi)存內(nèi)計算、近內(nèi)存計算是 AI 推動的方向,意味著傳統(tǒng)計算模型將發(fā)生變化。傳統(tǒng)架構(gòu)圍繞巨型計算引擎搭建,需要從附近內(nèi)存拉取數(shù)據(jù)。既然 SRAM 縮放已失效,行業(yè)將持續(xù)轉(zhuǎn)向新型內(nèi)存;更深層的問題是,現(xiàn)有 SRAM 使用方式是否已觸及架構(gòu)極限。Cerebras 的晶圓級引擎大幅增加片上內(nèi)存,突破部分約束。

即便如此,單裸片能容納的模型規(guī)模仍有上限,進(jìn)而引出核心問題:單晶圓能高效完成多少任務(wù)? 若堆疊晶圓或擴(kuò)大晶圓,架構(gòu)能否良好縮放,還是最終遇到同樣限制?

內(nèi)存墻不是一次性障礙,若架構(gòu)不變,模型每增大一級都會出現(xiàn)新壁壘。因此,設(shè)計決策必須聚焦系統(tǒng)可擴(kuò)展性,從單裸片到多裸片,再到集群。最初是 CPU 集群,之后是小芯片集群,再到板級集群,如今擴(kuò)展到整機柜作為統(tǒng)一計算資源。在納米、毫米、厘米、米甚至公里級,每個階段都會出現(xiàn)新挑戰(zhàn)。最終,資源劃分與管理方式?jīng)Q定能否突破反復(fù)出現(xiàn)的壁壘。

新型嵌入式內(nèi)存正逐步落地。

例如,磁阻 RAM(MRAM)縮放性好、漏電流低、耐久性強,有望替代 SoC 中的部分嵌入式閃存與 SRAM;阻變 RAM(ReRAM)因集成容易、成本較低,在嵌入式非易失存儲領(lǐng)域逐步普及。這些技術(shù)可補充但無法替代 L1/L2 緩存中的高性能 SRAM,但可替代部分控制器、MCU 與加速器中的嵌入式內(nèi)存。

高帶寬內(nèi)存(HBM)顯著提升 DRAM 帶寬,由多層 DRAM 堆疊而成,底層傳統(tǒng)上是面向處理器的裸片間物理層(PHY)。該基底裸片采用面向存儲單元而非邏輯的工藝,受限于功率密度與熱密度。若將基底裸片切換為邏輯優(yōu)化工藝,可支持更多功能、提供更高性能。

這樣可在 HBM 基底裸片與 GPU 之間實現(xiàn)更高帶寬的裸片間接口,利用富余帶寬連接更多 HBM,使 GPU 可訪問的 HBM 容量翻倍,或用于 I/O 小芯片提供更高外部帶寬,或二者結(jié)合。

在 SRAM 縮放不再自動受益的時代,架構(gòu)效率(尤其是互連與一致性層面)成為每平方毫米性能與每瓦性能的核心杠桿。通過智能管理緩存布局與流量行為,緩存可在不按比例增加 SRAM 面積的前提下,獲得足夠的內(nèi)存容量與帶寬收益。

結(jié)論

內(nèi)存墻越筑越高,短期看不到逆轉(zhuǎn)跡象。SRAM 縮放不太可能重回往日勢頭,必須尋找替代方案。3D 堆疊將更普及,尤其在成本下降后,但沒有萬能解藥。若高速內(nèi)存成為計算瓶頸,計算架構(gòu)必須更高效地利用現(xiàn)有內(nèi)存。

評論