看不見的振鈴:利用緩沖電路抑制降壓轉換器中的寄生效應

隨著電源設計日益追求更小尺寸、更高效率和更優散熱性能,噪聲問題往往被推遲到設計后期才處理,導致難以有效解決。雖然在設計初期采用Silent Switcher?穩壓器或對PCB布局進行優化有助于降低噪聲,但如果這些初步措施未能及時落實,可借助緩沖電路這種更為基礎的電路來有效緩解噪聲問題。

本文首先以同步降壓穩壓器為例,介紹了開關振鈴方面的問題。然后,文章闡述了如何設計和優化緩沖電路來抑制這種振鈴。我們將利用LTspice?和典型寄生模型來模擬標準PCB上出現的振鈴現象,并展示計算所得緩沖電路值對振鈴和整體效率的影響。

背景知識

現代DC-DC轉換器不斷朝著更高效率和更小尺寸的方向發展。為達成這一目標,常見做法是提高開關頻率。雖然如此一來,設計可以使用更小的電感和電容,但寄生效應(即元件和PCB走線產生的非預期電感和電容)的影響也更加突出。在較高開關速度下,電路與這些寄生效應的相互作用可能導致開關(SW)節點出現嚴重的電壓過沖和振鈴。

這種振鈴不僅會給FET帶來額外的電壓應力,還會產生不需要的電磁干擾(EMI)。EMI是一種電磁信號,通過電磁感應、靜電耦合或傳導來干擾系統運作。在汽車、醫療、測試與測量等行業中,EMI是一項關鍵設計挑戰。只有嚴格符合EMI標準,才能確保產品通過認證并及時上市。

了解寄生效應

降壓轉換器開關節點的電壓過沖和振鈴,是高開關速度與電路中的寄生電感和電容相互作用的直接結果。這些寄生效應由PCB走線和元件(尤其是FET)本身形成。

從本質上講,PCB走線和FET封裝的雜散電感與FET的寄生輸出電容(COSS)形成LC諧振電路。因此,MOSFET的布局和選型都是關鍵設計因素。

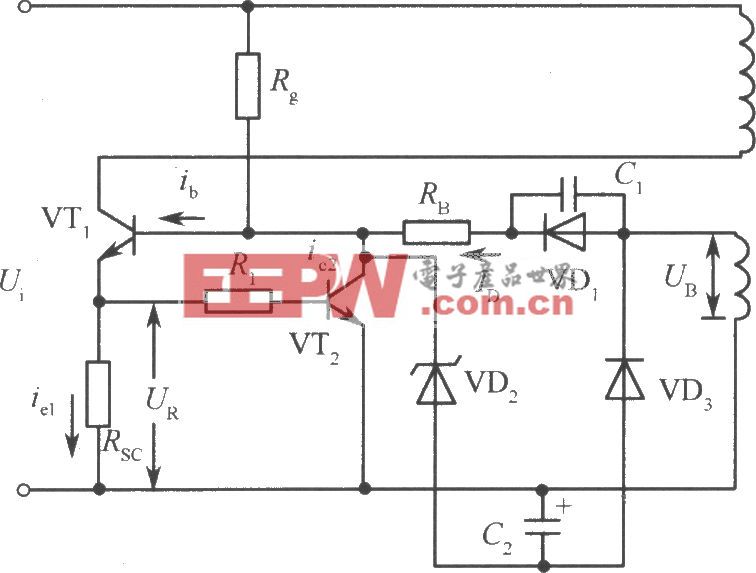

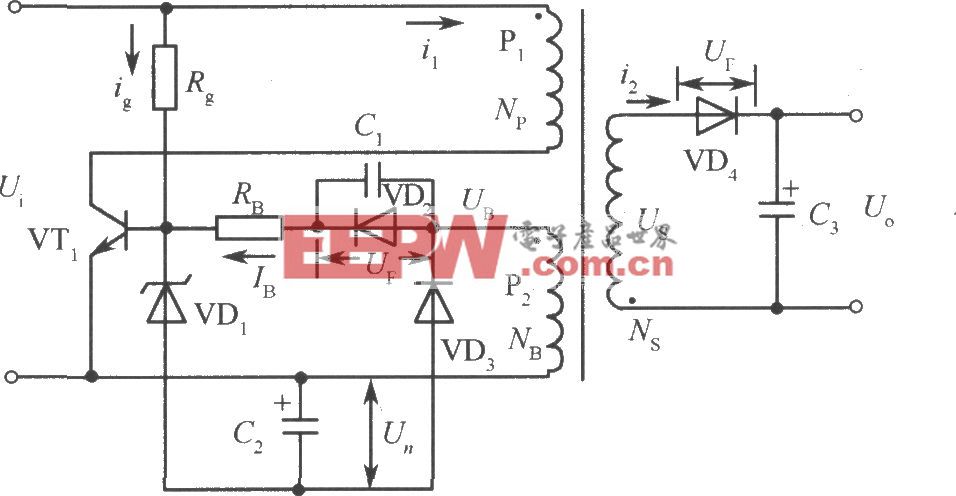

雜散電感的大小因設計而異,不過對于我們的示例仿真而言,功率級FET周圍的雜散電感假設為5 nH是一個合理的起點。如果布局不佳,該值可能會顯著升高,因為走線每延長25 mm(1英寸),雜散電感值最高可增加10 nH。圖1顯示了一個采用LTC3854的典型電源控制器電路,其中紅色部分為預期的寄生效應。

圖1.包含電路寄生效應的電源電路

緩沖電路設計:理論與計算

緩沖電路的定義及其工作原理

理解了開關活動所產生的噪聲及其涉及的寄生參數之后,便可介紹抑制這種多余能量的方法。緩沖電路通常為串聯電阻-電容(RC)網絡,可用于吸收開關節點上出現的電壓尖峰和振鈴。

緩沖電路的作用在于為寄生LC諧振電路產生的高頻能量提供一條受控的泄放路徑。當開關關斷時,緩沖電容開始充電,吸收原本會引起振鈴的能量。緩沖電阻隨后將該儲存的能量以熱量形式耗散掉,從而有效抑制振蕩。緩沖電路通過引入新的諧振頻率并為電路增加電阻,來降低振鈴的峰值電壓和持續時間,從而保護功率開關免受過壓應力的影響。

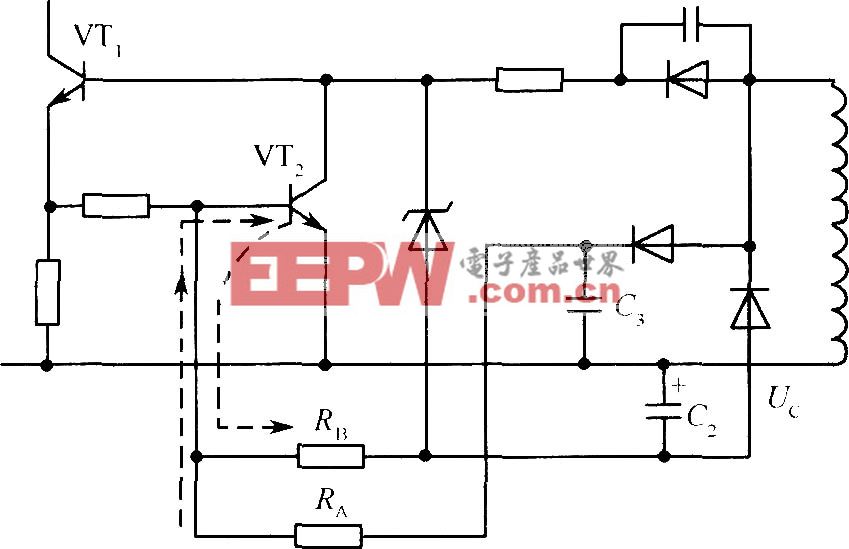

圖2展示了一個典型降壓轉換器,緩沖電路位于開關節點與地之間,且盡可能靠近MOSFET。

圖2.典型電源設計中緩沖電路的位置

緩沖電路的計算步驟

如測量技術部分所示,首先測量開關節點的振鈴頻率(即第一個尖峰的峰值到第二個尖峰的峰值)。提醒:本文的討論屬于仿真范疇,但對于實際電路板測量,必須關閉帶寬限制功能,并使用示波器短接地線以確保振鈴可見。本文稍后將簡要介紹所需的測量技術,供讀者參考。

在SW和GND之間增加一個電容,使振鈴頻率(fr)降低到上述測量值的大約一半。在此步驟中,建議嘗試不同的電容值。

將增加的電容值除以3,便得到寄生電容(CP)。

知道寄生電容后,寄生電感(LP)可計算如下:

特性阻抗計算如下:

為了減弱振鈴,需要使用一個緩沖電阻,其阻抗大致等于公式2中計算出的阻抗,通常為幾歐姆。

然后選取電容值:將公式3計算出的CP值乘以1到4的系數。

利用LTspice進行仿真和分析

掌握了噪聲產生、測量和初始緩沖電路值計算的基礎知識之后,下一步是對這些影響進行仿真。本節利用LTspice展示PCB寄生效應對開關節點振鈴和過沖的影響,以及緩沖電路的有效性。

我們將進行以下分析,比較降壓轉換器在有緩沖電路和無緩沖電路兩種情況下的運行狀況。

寄生效應建模:首先構建一個包含寄生參數的模型,以顯示沒有任何緩沖電路的情況下開關節點出現的振鈴和過沖。

初始緩沖電路影響:隨后使用初步計算出的緩沖電路值對電路進行仿真,以展示振鈴減弱效果。

緩沖電路優化:然后迭代調整緩沖電路元件的值,找到有效抑制振鈴與最小化功率損耗之間的平衡點。

圖3.測量技術的優劣對比

效率分析:最后比較有無優化緩沖電路兩種情況下降壓轉換器的整體效率,以量化緩沖電路的影響。

寄生效應建模與振鈴測量

LTC3854同步降壓控制器是一個很好的例子,用于說明糟糕的布局會如何引入顯著的寄生效應,導致開關節點出現振鈴現象。該器件采用外部FET,因此布局的影響尤為突出。對于此仿真,我們通過引入5 nH的寄生電感來模擬布局不佳的影響。這是一個合理的值,因為每25 mm的PCB走線可帶來10 nH或更多的寄生電感。

計算緩沖電路值之前,必須了解此問題的嚴重程度。這通常通過示波器監測開關節點來完成。為了準確捕捉上升電壓波形,應適當配置示波器的每格電壓以支持完整電壓范圍(0 V至VIN),并調整時基以查看單個躍遷。

使用恰當的探測技術是獲得準確測量結果的關鍵。一個常見錯誤是使用示波器探頭的長接地線,它自身就會引入寄生電感。此電感可能導致測量出現人為振鈴,從而對實際開關活動給出誤導性的表示。為了大幅降低環路電感并提升測量保真度,必須用短接地彈簧代替長引線。

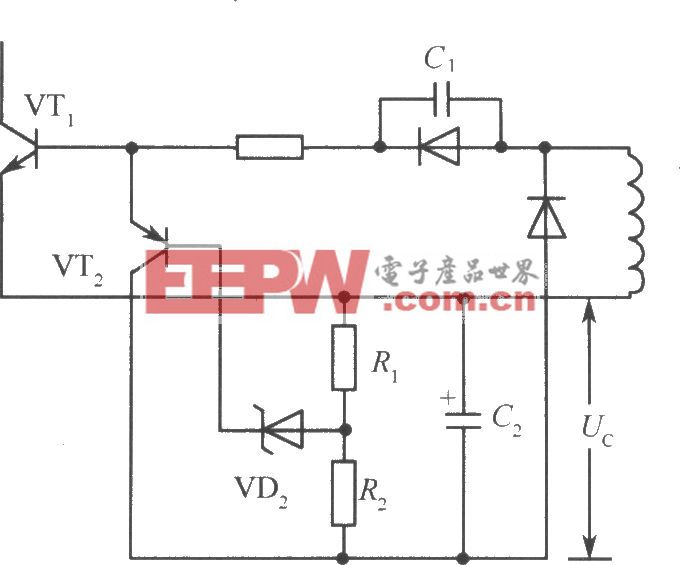

本文主要關注理論與仿真,對正確硬件測量技術的詳細講解不在本文范疇內,但這是一個十分重要的話題,值得專門探討。圖3中的圖像展示了測量結果的巨大差異,表明較長的接地引線可能人為引入嚴重的過沖和振鈴,從而導致對電路性能產生錯誤判斷。

無緩沖電路情況下的仿真結果

圖4.顯示電路板和元件寄生效應的原理圖

圖5.觀測到的開關節點及相關的過沖和振鈴

圖4顯示了降壓轉換器電路中建模的不同寄生電感和電容。圖5則展示了這些寄生參數對開關(SW)節點波形的影響。由這些元件形成的LC諧振電路會導致嚴重過沖和振鈴。

仿真結果顯示,電壓峰值超過18 V,遠高于預期的12 V。這種過沖是一個重大隱患,因為其幅度可能超過MOSFET的絕對最大額定電壓,進而可能損壞元件或降低其長期可靠性。振鈴也是一個問題,因為它表明MOSFET未在其明確定義的開/關狀態下工作。

圖6顯示該電路的整體效率為96.3%,乍一看似乎很高。但請注意,這一效率是在沒有緩沖電路的情況下實現的。以下部分將表明,增加緩沖電路(其對于抑制振鈴至關重要)會對效率產生微小且可量化的影響。

圖6.原始電路的效率

寄生模型和未經計算的緩沖電路

圖7顯示了與圖4相同的原理圖,但在開關節點與接地端之間增加了一個簡單的RC緩沖電路。請注意,緩沖電路值只是初始猜測值,尚未實際計算,因此并非最優值。

圖7.包含緩沖電路的原理圖

如圖8所示,開關節點波形得到了明顯改善。峰值過沖電壓降至14V,減少了4V,而且導通后出現的振蕩顯著減弱。然而,效率大幅降低至58.9%(見圖9),大部分損耗與緩沖電阻有關。這表明,未經優化的緩沖電路雖然可以減輕振鈴,但也會導致效率大幅降低。

圖8.引入緩沖電路后開關節點的振鈴

圖9.采用初始緩沖電路值時的效率

優化緩沖電路

現在,我們按照本文之前說明的計算方法來優化緩沖電路值。目標是選擇一個能夠有效抑制振鈴,但不會造成過大功率損耗的RC緩沖電路。

首先,確定電路的寄生LC元件。初始仿真(無緩沖電路)顯示振鈴頻率為23.41 MHz。

![]() 然后,在開關節點和接地端之間增加一個已知電容,觀察振鈴頻率的變化。在開關節點處使用14,000 pF電容后,新的仿真結果顯示,振鈴頻率降至12 MHz。利用諧振頻率公式fo = 1/(2 × PI√LC)可確定寄生電容。頻率的變化是由總電容增加引起的。新的總電容(Ctotal)為:

然后,在開關節點和接地端之間增加一個已知電容,觀察振鈴頻率的變化。在開關節點處使用14,000 pF電容后,新的仿真結果顯示,振鈴頻率降至12 MHz。利用諧振頻率公式fo = 1/(2 × PI√LC)可確定寄生電容。頻率的變化是由總電容增加引起的。新的總電容(Ctotal)為:

Ctotal = Cparasitic + Cadded

原始頻率(fold)與新頻率(fnew)之間的關系為:

求解Cparasitic:

這表明該電路具有約5,000 pF的寄生電容。利用寄生電容可計算出寄生電感:

該電路的阻抗計算如下:

緩沖電阻設置為大于上述特性阻抗的值,在本例中為標準值1.5 Ω。

接下來,緩沖電容Csnubber的大小通常至少應等于寄生電容值,最高可為該值的四倍。針對這一初始仿真,使用兩倍寄生電容的值以確保充分吸收能量,設置Csnubber = 2 × Cparasitic = 2 × 5,000 pF = 10,000 pF。

優化緩沖電阻和電容后,將這些值代入LTspice仿真中,觀察電路表現如何。

圖10.使用1.5 Ω+ 10,000 pF緩沖電路值時的開關節點振鈴情況

圖10顯示了使用1.5 Ω+ 10,000 pF緩沖網絡后得到的波形。正如優化設計所預期的那樣,振鈴已顯著減弱。使用計算得到的這些緩沖電路值后,過沖電壓也從18 V以上降低到17.2 V。雖然仍有一定的過沖,但此結果凸顯了緩沖電路設計中的固有權衡:完全消除過沖和振鈴所需的緩沖電路值,通常會導致功率損耗加大和效率降低。

此外,現在整體效率為94.8%(見圖11),與使用未經計算的緩沖電路時的58.9%相比,提升幅度非常顯著。使用緩沖電路必定會對效率產生一定影響,因為電阻會消耗少量功率。然而,只要根據寄生LC諧振電路優化元件值,就能將其對效率的影響降至最低。

圖11.使用計算得到的1.5 Ω+ 10,000 pF緩沖電路值時的電路效率

結語

了解并抑制開關節點振鈴是設計可靠開關穩壓器的關鍵步驟。如本文所述,這種高頻噪聲并非固有缺陷,而是由PCB走線電感和開關元件電容形成的寄生LC諧振電路的直接結果。

采用系統分析方法,對未加抑制的振鈴頻率和相關的電壓過沖進行精準仿真,這個問題便可迎刃而解。通過這種方法可計算出準確的緩沖網絡值,其中電阻通過匹配寄生阻抗來使電路達到臨界阻尼狀態,而電容則起到能量吸收器的作用。

仿真示例清楚地表明,精心設計的緩沖電路是一種簡潔而有效的解決方案。它以較小且可控的功率損耗為代價,換取EMI性能和系統可靠性的顯著提升。總之,通過整合這種簡單而強大的RC網絡,噪聲大、易受干擾的電源就能迅速轉變為噪聲低、穩定可靠的電源,確保最終產品經久耐用且符合標準。

評論