基于Verilog HDL的DDS設計與仿真

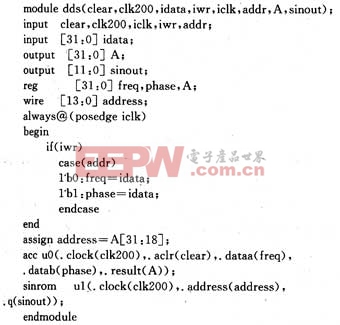

若需要利用NIOSⅡ對其進行控制,需要并將DDS模塊加載到NIOSⅡ的系統中。例如,通過NIOSⅡ為DDS模塊的頻率控制字freq和相位控制字phase置數。此時DDS的代碼應改為:

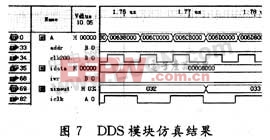

模塊的輸入端口添加了寫信號iwr、地址信號addr和與NIOSⅡ同步的時鐘信號iclk,這樣是為了將DDS模塊連接到Avalon總線上,利用總線和NIOSⅡ進行通信。加載到NIOSⅡ系統之前,需要將該模塊進行仿真和調試。仿真結果如圖7所示。

至此DDS的數字部分已經完成。

對于整個模塊的驅動時鐘,若時鐘源器件的頻率不符合實際需要,需要再設計一個倍(分)頻器將其倍頻或是分頻。例如現有時鐘源為50 MHz,可以使用FPGA中的PLL(鎖相環)實現4倍頻得到200 MHz。

評論