雙網傳真機的編譯碼電路設計與實現

摘要:對雙網數字傳真機硬件系統中的編碼和譯碼電路進行設計,并采用FPGA芯片進行系統實現和驗證。其中的編譯碼電路分別采用兩級編碼和快速譯碼的思路,利用硬件描述語言設計和仿真,簡化了邏輯電路的實現。驗證測試表明,該電路增強了系統的穩定性和可靠性,提高了編譯碼效率,縮短了開發周期。

關鍵詞:編譯碼電路;FPGA;碼表;雙網傳真機

0 引言

傳真通信規程是將要掃描的電平信號值進行A/D轉換,再經過圖像二值化處理,表示成連續交替黑白點的數據序列(I/O序列),再對該數據序列進行編碼后,調制發送;接收端對收到的編碼數據信號解調后進行譯碼,最后由熱敏頭打印輸出。

在傳真通信中,對傳真圖像數據進行編碼和譯碼是傳真通信的關鍵技術。改進的Huffman碼(MHC)是ITU—T.4向各國推薦的一維標準碼,主要應用于三類傳真機上。MHC碼是一種常用的變長碼,其信源的消息與碼字之間的關系是一對一的,是信息保持型的壓縮方法。雙網傳真系統完成與Internet和PSTN網絡的傳真通信,采用嵌入式系統的設計思路劃分軟硬件。其中,傳真協議采用軟件實現,傳真編譯碼和外圍設備控制器采用硬件實現,以降低設計復雜度,提高傳真效率。

1 傳真機硬件系統模型

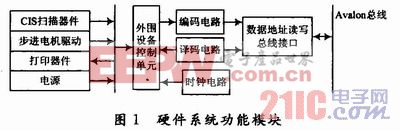

硬件電路模塊應包括:CIS掃描電路模塊(A/D轉換)、編碼電路模塊(圖像二值化處理)、譯碼電路模塊、打印電路模塊、步進電機驅動電路模塊及時鐘電路模塊。并以NiosⅡ軟核處理器、CIS掃描器件、步進電機、TPH打印器件為硬件平臺,通過FPGA實現硬件電路模塊。上層軟件通過讀寫寄存器來控制外圍設備和編譯碼電路,完成編碼數據的讀取和譯碼數據的寫入。圖1給出了硬件系統功能模塊劃分邏輯圖。

其中,時鐘電路用來產生掃描、打印及步進電機所需的時序信號;由時鐘電路產生的CIS時鐘周期為2.6μs,打印時鐘周期為4.96μs,步進電機時鐘周期為10 ms。數據地址讀寫總線接口與NiosⅡ處理器直接交互各種控制命令及讀寫數據,產生外圍設備的工作使能信號,通過地址選通信號,完成各個模塊與NiosⅡ處理器之間數據的交互。

2 外圍設備控制單元

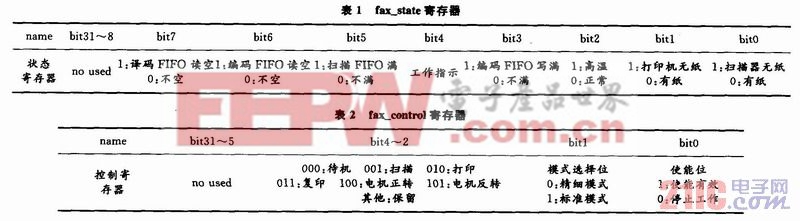

外圍設備的控制主要是通過對CIS掃描器件、TPH打印器件和步進電機發出相應的控制時序信號完成掃描、打印和步進電機的驅動等功能。該部分采用硬件實現可以產生超過定時中斷周期的更小周期的時序信號和時序要求精確的驅動信號,同時可以通過配置控制寄存器,對掃描和打印的功能進行選擇,上層軟件通過狀態寄存器來判斷電路的工作狀態。表1和表2給出了寄存器的詳細描述。

2.1 CIS掃描及A/D轉換

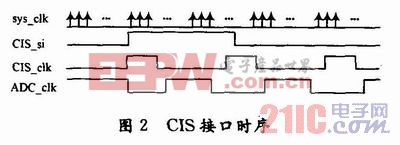

設計采用的CIS器件具有最高1.7 MHz的掃描時鐘,且有效掃描寬度為216 mm(A4紙的寬度),每行有1728個掃描點。FPGA片內的數字邏輯產生驅動信號CIS_si和CIS_clk,并將模擬信號接入A/D轉換器的模擬輸入端口,由FPGA片內數字邏輯實時對A/D轉換器的輸出進行采集。圖2給出了CIS接口時序。其中,CIS_si為行啟動信號,每行有1728個掃描點,每隔10ms啟動一次CIS_si。由于掃描最快能達到1.8ms/line,而打印最快只能達到10 ms/line,所以掃描完成后且預留出步進電機工作的時間,這樣就能滿足該系統的要求。CIS_clk為2.6μs的掃描時鐘,占空比為0.254。ADC_clk為AD采樣時鐘,周期與CIS_clk相同,占空比為0.046。

A/D轉換的原理是通過CIS掃描器件把原稿的光信號轉化為電信號,將CIS掃描器件獲得的模擬電信號通過A/D轉換器件轉化為8 b的數字信號在ADC_clk的下降沿送入掃描數據緩沖區。

評論