基于Cadence_Allegro的高速PCB設計信號完整性分析與仿真

2 基于Cadence_Allegro的仿真結果及分析

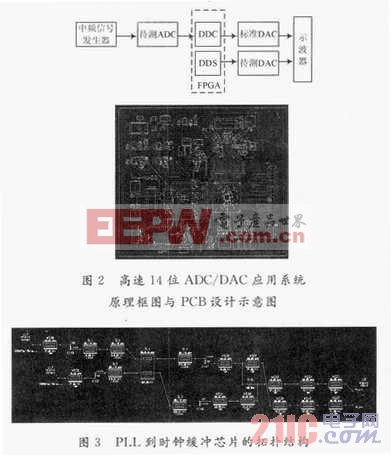

2.1 高速14位ADC/DAC應用系統(tǒng)簡介

如圖2所示,該應用系統(tǒng)可做ADC/DAC芯片驗證,基于Cyclone2系列的FPGA,可實現(xiàn)DDC,DDS功能。實際應用中待測ADC選用Linear公司14位105 MS/s的芯片LTC2284,DAC芯片采用AD公司14位、210 MSPS的芯片AD9783,系統(tǒng)PCB設計如圖2所示。本文引用地址:http://www.cqxgywz.com/article/178953.htm

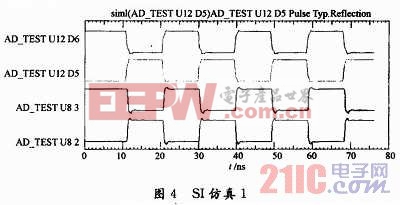

2.2 對AD時鐘信號的反射仿真與分析

仿真主要基于IBIS模型,它是用于描述I/O緩沖信息特性的模型,它可以將一個輸出輸入端口的行為描述分解為一系列的簡單的功能模塊,由這些簡單的功能模塊就可以建立起完整的IBIS模型。本應用系統(tǒng)時鐘是由FPGA軟件倍頻后經(jīng)由時鐘緩沖器件分配到ADC,DAC網(wǎng)絡的。提取的由FPGA鎖相環(huán)到時鐘緩沖芯片的拓撲結構如圖3所示。

對其SI仿真如圖4所示。

評論