淺析AD9522時鐘分頻電路原理

在集成度高度發展的今天,不能靠多個晶振源來解決問題,而且一旦晶振固定那么它的靈活性和可移植性必然受到很大影響,所以一些時鐘分頻芯片應運而生,今天我們將舉一個很有代表性的AD9522時鐘分頻芯片的典型應用來達到一個拋磚引玉的作用。

本文引用地址:http://www.cqxgywz.com/article/174635.htm一、AD9522簡介

1.外部特性

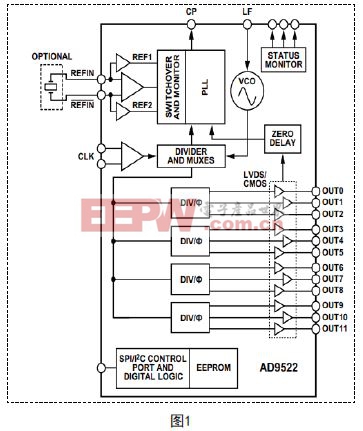

A D 9 5 2 2是一個多路時鐘輸出和分配功能的芯片,本身支持亞皮秒抖動性能,在芯片內部還集成了PLL(PhaseLockedLoop)和VCO(壓控振蕩器)。VCO的調諧范圍是 2.02GHz~2.335 GHz.AD9522串行接口支持SPI與I2C的數據總線,芯片內部的EEPROM可通過串口進行編程,可以用來存儲用戶配置的寄存器數據從而使輸入時鐘分頻。AD9522具有12路的LVDS電平輸出,可以分成4組,每組輸出都有分頻器,分頻比1-32之間可以在其范圍內隨意設置。如圖1所示。

2.內部特性

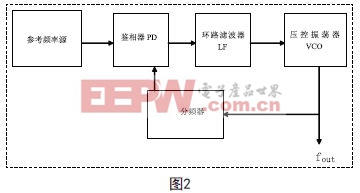

AD9522外部的輸入時鐘是晶振供給的,內部時鐘的倍頻和分頻都是由鎖相環PLL和壓控振蕩器VCO控制的。例如壓控振蕩器給出一個信號,一部分作為輸出,另一部分通過分頻與PLL產生的本振信號作相位比較,為了保持頻率不變,就要求相位差不發生改變,如果有相位差的變化,則PLL的電壓輸出端的電壓發生變化,去控制VCO,直到相位差恢復,達到鎖頻的目的。如圖2.

二、單片機配置

1.寄存器配置

我們提到了AD9522可以配置SPI與I2C的數據總線來達到分頻的目的,那么配置數據總線就可以用單片機來配置了。我們選用C8051F320作為配置AD9522的內部寄存器,原因是單片機編程比較直觀也比較容易。如圖3.

寫完成后設置斷點觀測寫入和讀取值是否相同,驗證好讀取沒有問題后開始配置寄存器。配置的時候要注意的是0×18地址寄存器配置鎖定檢測周期數選擇大一些,有可能一些設置參數或者環路濾波帶寬設置導致鎖定時間比較長,導致讀取0 x 1 F地址時鎖定狀態不是最終狀態,現在設置該寄存器為0×66,將檢測周期數設置為最大值255.

VCO校驗需要先設置0×180>為0然后更新,再設置0×180>為1再次更新。等待校驗完成讀取0x1F地址數據。0x1D7>需要設置為0,S t a t u s引腳顯示狀態才為0 x 1 7地址配置狀態。否則引出的時鐘觀測不到。配置完成后讀取0x1f地址狀態,配置完成后需要等待一定時間再讀取0x1f地址數據,因為vco校驗需要一定時間,讀取太快會導致讀取狀態不正確。

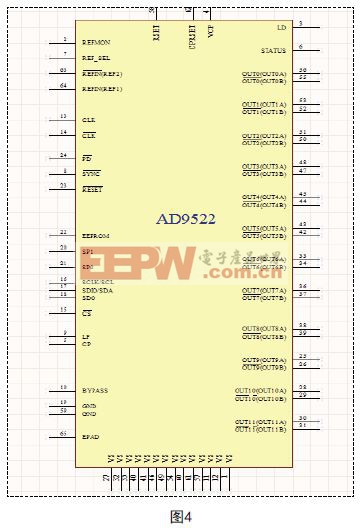

如圖4所示,在引腳上下拉方面VCP需要上拉,PD,SYNC,RESET需要上拉,使這些引腳無效。EEPROM使內部寄存器數值不從EPROM加載。SP1,SP0需下拉,將內部寄存器數據加載配置模式設置為I2C加載。CS下拉使數據片選信號一直有效。REF_SEL下拉選擇輸入參考時鐘為refrence1.

評論