堆疊硅片互聯技術的可行性

1. 概要

本文引用地址:http://www.cqxgywz.com/article/127572.htm為盡早推出 28nm 高容量 FPGA 產品,賽靈思 (Xilinx) 通過以下工作滿足了關鍵需求:

充分利用 FPGA 的重復結構創建分區,并將分區按編號組合起來以創建單個產品,相對于采用大型單片產品而言,在工藝節點生命周期的早期即實現了高良率特性。

使用具有高可靠性的微凸塊,將硅片連接至硅中介層。

使用 TSV 技術和在大批量生產中獲得全面驗證的高密度互聯技術構成中介層,實現低時延的芯片間通信和倒裝片封裝。

使用大面積標準焊接凸塊,實現從中介層到下一級的高可靠性連接功能。

堆疊硅片互聯技術能充分滿足大批量生產需求,從而確保 28nm FPGA 產品能夠具備卓越的高可靠性和大容量優勢。賽靈思將一系列業經驗證的大批量生產技術完美結合在一起,為需要大容量FPGA 的系統提供了高度創新的解決方案。

2. 挑戰性綜述

賽靈思的 Virtex-7 產品包含多達 200 萬個可用的邏輯門,與 Virtex-6 系列相比,可將每個門的功耗降低 50%。此外,Virtex-7 系列還支持速率高達 28Gbps 的高速 SERDES,并集成了大量 DSP 模塊。

較大容量 FPGA 產品有潛力成為系統設計的核心,而不是僅具備支持隨機門的功能,因而可為客戶提供眾多顯著優勢,如在各種系統類型和應用細分領域中實現全新的產品系列。

需要解決的一大關鍵問題領域就是,如何用新的技術節點改進超大尺寸產品的低良率問題。隨著缺陷密度水平的降低,良率會隨著時間的推移不斷上升,但這需要 18 到 24 個月的時間。

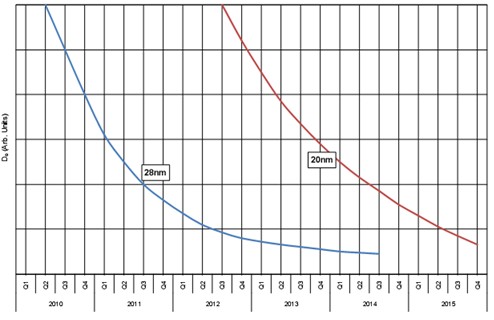

下圖顯示了 28nm 和 20nm 技術在缺陷密度方面的改進情況。

圖 1

28nm 和 20nm技術的缺陷密度水平

新技術缺陷密度水平的降低相對較快,但也要 18 到 24 個月才能實現大尺寸芯片的高良率。賽靈思采用的方案是通過 FPGA 產品的重復結構實現 N 個較小芯片,此外, N 可以是 2、4 或更多,N 個芯片組裝在一起就形成了一個有著相同特性的大型芯片。

這就克服了分別封裝 N 個芯片所帶來的挑戰,因而不會出現芯片、封裝以及開發板之間來回出現的延遲,有效避免了高功耗和延遲過長的問題。

由于使用了較小尺寸的芯片,我們能夠快速提高晶圓產量,避免了與大尺寸芯片相關的良率下降問題。

隨著缺陷密度水平的降低,多芯片與單芯片解決方案之間的凈良率差異將減小。但是,使用較小芯片的性能優勢仍保持不變。

大尺寸芯片上的大容量 FPGA 互連長度非常長,對于采用 28nm 工藝的緊密柵距互連結構而言,物理參數稍有變化就會對關鍵路徑的延遲產生較大影響。隨著技術不斷成熟,諸如TSMC等晶圓廠商將逐漸縮小延遲差異。

因而,我們面臨的關鍵挑戰是,如何使用多芯片方案,在新技術節點剛剛可用的早期階段實現低延遲互連。

評論