- XUP(Xilinx大學(xué)計劃部)攜手Digilent China(上海德致倫)于2012年3月4日,在上海浦東軟件大廈Xilinx上海分公司舉辦首期TTP(Target Teaching Platform)課程培訓(xùn)。

- 關(guān)鍵字:

Digilent FPGA

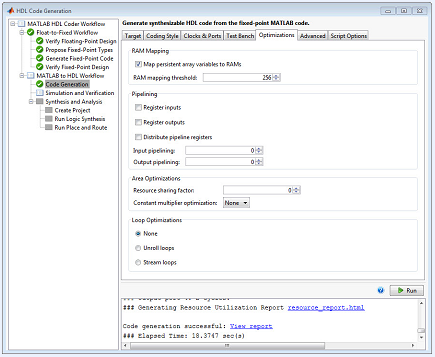

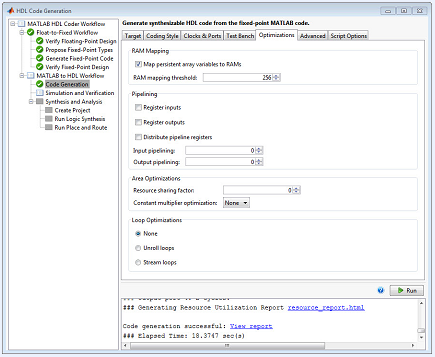

- MathWorks近日宣布推出HDL Coder,該產(chǎn)品支持MATLAB 自動生成 HDL 代碼,允許工程師利用廣泛應(yīng)用的 MATLAB 語言實現(xiàn) FPGA 和 ASIC 設(shè)計。MathWorks還宣布推出了HDL Verifier,該產(chǎn)品包含用于測試 FPGA 和 ASIC 設(shè)計的 FPGA 硬件在環(huán)功能。有了這兩個產(chǎn)品,MathWorks現(xiàn)在可提供利用 MATLAB 和 Simulink 進行 HDL 代碼生成和驗證的能力。

- 關(guān)鍵字:

MathWorks FPGA HDL

- 為創(chuàng)新設(shè)計和構(gòu)建需要大量帶寬的應(yīng)用,Altera公司(NASDAQ: ALTR)今天宣布,在世界上首次演示公司的光FPGA技術(shù)。與Avago技術(shù)公司聯(lián)合開發(fā),這一演示展示了Altera的光互連可編程器件怎樣大幅度提高互連帶寬,同時減小系統(tǒng)復(fù)雜度,降低功耗和價格。這一技術(shù)演示是Altera公司最近的系列創(chuàng)新之一,這些創(chuàng)新包括,業(yè)界為FPGA開發(fā)的第一個OpenCL程序,以及28-Gbps收發(fā)器技術(shù),實現(xiàn)了業(yè)界最高數(shù)據(jù)速率以及優(yōu)異的信號完整性。Altera于上一季度在部分用戶中進行演示,并將于2012年3月6

- 關(guān)鍵字:

Altera FPGA

- 利用FPGA實現(xiàn)大型設(shè)計時,可能需要FPGA具有以多個時鐘運行的多重數(shù)據(jù)通路,這種多時鐘FPGA設(shè)計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數(shù)、異步時鐘設(shè)計和時鐘/數(shù)據(jù)關(guān)系。設(shè)計過程中最重要的一步是確定要

- 關(guān)鍵字:

FPGA 大型 策略 多時鐘

- 摘要:以基于靜態(tài)隨機存儲器(SRAM)的現(xiàn)場可編程門陣列(FPGA)為例,在傳統(tǒng)的三次測試方法的基礎(chǔ)上提出了一種新穎的針對FPGA互聯(lián)資源的測試方法。該方法運用了層次化的思想,根據(jù)開關(guān)矩陣中可編程互聯(lián)點(PIP)兩端連線資

- 關(guān)鍵字:

FPGA 互聯(lián) 方法 資源測試

- 摘要:由于超級電容器單體性能參數(shù)的離散性,當(dāng)多個單體串聯(lián)組成電容器組時,在充放電過程中容易造成過充或過放現(xiàn)象,嚴(yán)重危害超級電容器的使用壽命。文中提出以FPGA為檢測、控制單元,對電容進行有效地充放電控制,

- 關(guān)鍵字:

FPGA 超級電容 充放電

- FPGA配置電路可以看成用戶設(shè)計和硬件電路之間的連接紐帶,最終目的是在一定外部條件下,準(zhǔn)確快速地實現(xiàn)FPGA系統(tǒng)配置。在FPGA的配置系統(tǒng)中,軟件編程由FPGA提供商提供,設(shè)計人員要掌握其操作方法,將配置數(shù)據(jù)從PC加載

- 關(guān)鍵字:

Xilinx FPGA 配置電路 分類

- 摘要:文中介紹了一種基于FPGA的數(shù)字秒表設(shè)計方法。采用VHDL硬件描述語言,運用ModelSim等EDA仿真工具。該設(shè)計具有外圍電路少、集成度高、可靠性強等優(yōu)點。最后經(jīng)實驗驗證,該數(shù)字秒表計時準(zhǔn)確,輸入信號能準(zhǔn)確控制秒

- 關(guān)鍵字:

FPGA 數(shù)字秒表 設(shè)計方法

- 今日相容于IEEE 802.15.4且適用于ZigBee的無線射頻收發(fā)器、微控制器及系統(tǒng)單芯片(SoC)半導(dǎo)體裝置已相當(dāng)普及。高度整合的多功能SoC解決方案是促成ZigBee無線網(wǎng)絡(luò)得以廣泛運用在眾多應(yīng)用中的重要因素,包括工業(yè)監(jiān)控、家

- 關(guān)鍵字:

ZigBee SoC

- 摘要:分析了串聯(lián)諧振的原理并通過推導(dǎo)得出諧振電容兩端電壓的關(guān)系式,結(jié)合目前國內(nèi)高壓電纜耐壓測試的發(fā)展現(xiàn)狀,證明了變頻串聯(lián)諧振試驗方法的優(yōu)越性。對于控制部分,利用現(xiàn)場可編程門陣列(FPCA)實現(xiàn)了自動頻率跟蹤

- 關(guān)鍵字:

測試 電源 研制 電纜 交聯(lián) FPGA 高壓 基于

- 全球可編程平臺領(lǐng)導(dǎo)廠商賽靈思公司(Xilinx, Inc.(NASDAQ: XLNX))今日宣布行業(yè)第一個28nm FPGA器件已經(jīng)針對主要客戶開始量產(chǎn), 該發(fā)布再次為行業(yè)樹起了另一個重要里程碑。Kintex?-7 FPGA的正式量產(chǎn),是賽靈思以可編程邏輯器件(PLD)行業(yè)歷史最快速度交付新產(chǎn)品的出色執(zhí)行中, 繼已成功交付數(shù)以千計的最新7系列產(chǎn)品樣片之后, 再次邁出的嶄新一步。這一成就使賽靈思的客戶能夠比以往任何時候都更快地開始投產(chǎn)他們自己的產(chǎn)品, 同時也能比以往任何時候更快地滿足他們客戶的需求。

- 關(guān)鍵字:

賽靈思 FPGA

- 基于IP復(fù)用和SOC技術(shù)的微處理器FSPLCSOC模塊設(shè)計,1 引言 文中采用IP核復(fù)用方法和SOC技術(shù)基于AVR 8位微處理器AT90S1200IP Core設(shè)計專用PLC微處理器FSPLCSOC模塊。隨著芯片集成程度的飛速提高,IC產(chǎn)業(yè)中形成了以片上系統(tǒng)SOC(System-on-Chip)技術(shù)為主的設(shè)計方式。一

- 關(guān)鍵字:

FSPLCSOC 模塊 設(shè)計 微處理器 技術(shù) IP 復(fù)用 SOC 基于

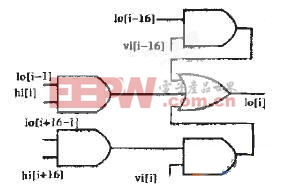

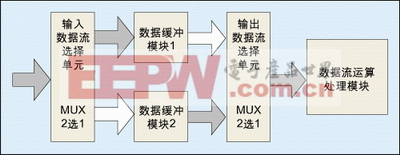

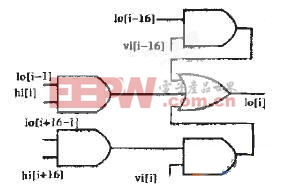

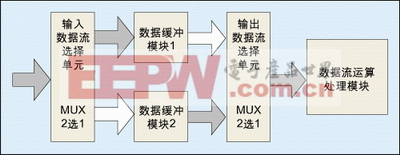

- FPGA/CPLD常用的四種設(shè)計方法,FPGA/CPLD的設(shè)計思想與技巧是一個非常大的話題,本文僅介紹一些常用的設(shè)計思想與技巧,包括乒乓球操作、串并轉(zhuǎn)換、流水線操作和數(shù)據(jù)接口的同步方法。希望本文能引起工程師們的注意,如果能有意識地利用這些原則指導(dǎo)日

- 關(guān)鍵字:

方法 設(shè)計 常用 FPGA/CPLD

- 遙控器有許多不同的尺寸和形狀,而且選擇的無線技術(shù)也不盡相同。作為產(chǎn)品配件,其廣泛用于消費類電子領(lǐng)域,如電視 ...

- 關(guān)鍵字:

SoC 發(fā)射器 RF 遙控器

- · 最新 SoC 不但可幫助運營商及制造商輕松高效地發(fā)揮小型蜂窩基站的優(yōu)勢,同時還可為通過提升容量實現(xiàn)差異化的應(yīng)用提供最佳平臺;

· 支持同步雙模式,可幫助運營商簡化從 2G 至 3G甚至 4G 的升級,并可降低運營成本和資本支出;

· 首款集成 ARM? Cortex? -A15 內(nèi)核的無線基礎(chǔ)設(shè)施 SoC,與現(xiàn)有解決方案相比,可在功耗降低一半的情況下提高集成度與性能。

- 關(guān)鍵字:

TI SoC TCI6636

soc-fpga介紹

您好,目前還沒有人創(chuàng)建詞條soc-fpga!

歡迎您創(chuàng)建該詞條,闡述對soc-fpga的理解,并與今后在此搜索soc-fpga的朋友們分享。

創(chuàng)建詞條

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473