fpga-to-asic 文章 最新資訊

華虹NEC推出高效nvSOC產(chǎn)品原型平臺(tái)

- 世界領(lǐng)先的純晶圓代工廠之一,上海華虹NEC電子有限公司(以下簡(jiǎn)稱“華虹NEC”)日前宣布成功推出nvSOC產(chǎn)品原型平臺(tái),這一平臺(tái)的推出可以幫助客戶高效創(chuàng)建SOC和ASIC原型,大大縮短客戶SOC產(chǎn)品開發(fā)周期和減少設(shè)計(jì)風(fēng)險(xiǎn)。 nvSOC平臺(tái)的硬件主要由通用FPGA芯片和華虹NEC特有的平臺(tái)核心IP芯片構(gòu)成,其中平臺(tái)核心IP芯片是指集成了華虹NEC 某一種NVM(Non Volatile Memory, 包括Flash,EEPROM,OTP等)工藝平臺(tái)的NVM模塊和基礎(chǔ)模擬/

- 關(guān)鍵字: 華虹NEC 晶圓代工 SOC ASIC

一種基于FPGA的AGWN信號(hào)生成器的設(shè)計(jì)

- 在通信系統(tǒng)中分析計(jì)算系統(tǒng)抗噪聲性能時(shí),經(jīng)常假定信道噪聲為加性高斯型白噪聲(AGWN)。本文就是通過分析AG...

- 關(guān)鍵字: FPGA AGWN 信號(hào)生成器

基于FPGA的數(shù)據(jù)采集控制模塊設(shè)計(jì)

- 0 引 言

數(shù)據(jù)采集和控制系統(tǒng)是對(duì)生產(chǎn)過程或科學(xué)實(shí)驗(yàn)中各種物理量進(jìn)行實(shí)時(shí)采集、測(cè)試和反饋控制的閉環(huán)控制,它在工業(yè)控制、軍事電子設(shè)備、醫(yī)學(xué)監(jiān)護(hù)等許多領(lǐng)域發(fā)揮著重要作用。其中,數(shù)據(jù)采集部分尤為重要,而傳統(tǒng) - 關(guān)鍵字: FPGA 數(shù)據(jù) 采集控制 模塊設(shè)計(jì)

基于FPGA的級(jí)聯(lián)結(jié)構(gòu)FFT處理器的優(yōu)化設(shè)計(jì)

- 0 引 言

數(shù)字信號(hào)處理主要研究采用數(shù)字序列或符號(hào)序列表示信號(hào),并用數(shù)字計(jì)算方法對(duì)這些序列進(jìn)行處理,以便把信號(hào)變換成符合某種需要的形式。在現(xiàn)代數(shù)字信號(hào)處理中,最常用的變換方法就是離散傅里葉變換(DFT), - 關(guān)鍵字: FPGA FFT 級(jí)聯(lián) 處理器

對(duì)基于FPGA的作戰(zhàn)系統(tǒng)時(shí)統(tǒng)的研究與設(shè)計(jì)

- O引言作戰(zhàn)系統(tǒng)時(shí)間的統(tǒng)一同步(時(shí)統(tǒng))的重要性越來越得到重視,只有保證整個(gè)系統(tǒng)處在同一時(shí)間的基準(zhǔn)...

- 關(guān)鍵字: FPGA 作戰(zhàn)系統(tǒng) 時(shí)統(tǒng)

追新逐熱還是腳踏實(shí)地?跟上技術(shù)發(fā)展的步伐

- 我真的需要那種技術(shù)嗎?我現(xiàn)在應(yīng)該購(gòu)買嗎?如果我不購(gòu)買,是不是就會(huì)處于劣勢(shì)?我會(huì)不會(huì)因?yàn)樽龀鲥e(cuò)誤的決定而出局?即便不想成為先行者,同行的壓力與技術(shù)變化的速度,也會(huì)使我們不斷面對(duì)類似的更多問題。最終,我們還是得想辦法回到正確的技術(shù)軌道上來。 研究、保持使用最新技術(shù)以及直覺,都將有助于縮小這些決定的范圍,不過最終還是得在冒險(xiǎn)一試與放棄之間做出選擇。即使有些不情愿或者也許有點(diǎn)晚,我們?nèi)匀粨碜o(hù)變革。 在消費(fèi)類電子產(chǎn)品前沿,事情并不總是那么順理成章的。無論行業(yè)評(píng)論員的權(quán)威意見是什么,也不管他們給予怎樣

- 關(guān)鍵字: Altium FPGA 設(shè)計(jì)工具

超越 SoC 的設(shè)計(jì)創(chuàng)新

- 大多數(shù)軟、硬件工程師都很熟悉 FPGA,這點(diǎn)應(yīng)該勿庸置疑。這種熟悉不見得是實(shí)質(zhì)性的熟悉,而是從概念上比較了解,也就是說 FPGA 功能的快速發(fā)展和成本的不斷下降是大家都不容忽略的優(yōu)勢(shì)。同時(shí),他們也認(rèn)識(shí)到這種可編程器件顯然能方便地作為各種數(shù)字電路以及邏輯處理的高靈活度、低成本的載體。 基本說來,在設(shè)計(jì)方案中發(fā)揮 FPGA 的功能就是簡(jiǎn)單地映射出所需的邏輯,然后將其下載至適當(dāng)容量大小的器件中。這有些像大型處理器系統(tǒng)主體設(shè)計(jì)的輔助支持工作,而且在該層面上也確實(shí)發(fā)揮著自身的支持性作用。 近期一些應(yīng)

- 關(guān)鍵字: SoC FPGA

基于FPGA的8段數(shù)碼管動(dòng)態(tài)顯示IP核設(shè)計(jì)

- 設(shè)計(jì)基于FPGA的8段數(shù)碼管動(dòng)態(tài)顯示IP核,介紹8段數(shù)碼管內(nèi)部結(jié)構(gòu)及其驅(qū)動(dòng)顯示方式和IP核設(shè)計(jì)方法,給出8段數(shù)碼管動(dòng)態(tài)顯示IP核的Verilog HDL程序源代碼及其C語言驅(qū)動(dòng)程序。此IP核可例化成1~8個(gè)共陰極(或共陽極)數(shù)碼管控制器,能方便地控制1~8個(gè)數(shù)碼管同時(shí)顯示數(shù)字和小數(shù)點(diǎn)位。測(cè)試結(jié)果表明,該IP核工作可靠、穩(wěn)定,可直接應(yīng)用于電子設(shè)計(jì)中。

- 關(guān)鍵字: FPGA 8段數(shù)碼管 動(dòng)態(tài)顯示 IP核

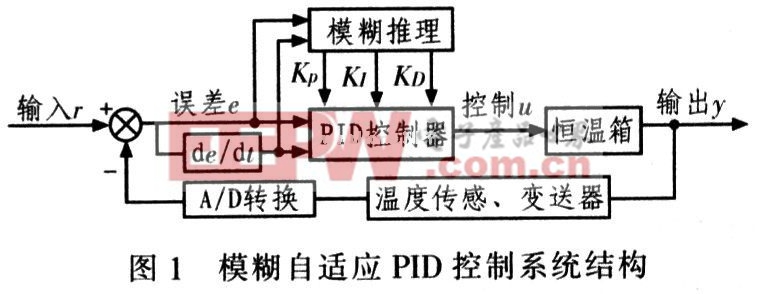

基于FPGA的溫度模糊自適應(yīng)PID控制器的設(shè)計(jì)

- 針對(duì)某恒溫箱控制系統(tǒng)中存在的非線性、時(shí)變等特點(diǎn),結(jié)合傳統(tǒng)PID與現(xiàn)代模糊控制理論,以EP1C12型FP-GA為核心控制器,采用模塊化思想,設(shè)計(jì)并實(shí)現(xiàn)溫度模糊自適應(yīng)PID控制。實(shí)際運(yùn)行結(jié)果表明,采用該方法可明顯改善控制效果,在簡(jiǎn)化設(shè)計(jì)的同時(shí),也可提高系統(tǒng)的運(yùn)算速度和可靠性。

- 關(guān)鍵字: PID 控制器 設(shè)計(jì) 適應(yīng) 模糊 FPGA 溫度 基于

基于FPGA技術(shù)的數(shù)字相關(guān)器的設(shè)計(jì)與實(shí)現(xiàn)

- 1 引 言 同步在通信系統(tǒng)中占有非常重要的地位,同步系統(tǒng)性能的高低在很大程度上決定了通信系統(tǒng)的質(zhì)量,甚至通信的成敗。相關(guān)器是同步系統(tǒng)的關(guān)鍵部件之一,因此,要求相關(guān)器須有比其它部件更高的可靠性。

- 關(guān)鍵字: FPGA 數(shù)字相關(guān)器

fpga-to-asic介紹

您好,目前還沒有人創(chuàng)建詞條fpga-to-asic!

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga-to-asic的理解,并與今后在此搜索fpga-to-asic的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga-to-asic的理解,并與今后在此搜索fpga-to-asic的朋友們分享。 創(chuàng)建詞條

熱門主題

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司