dsp+fpga 文章 最新資訊

針對低成本視頻和DSP 系統(tǒng)開發(fā) Xilinx再推兩款XtremeDSP 開發(fā)平臺

- XtremeDSP DSP入門套件 XtremeDSP視頻入門套件 3月12日,北京 -全球可編程邏輯解決方案領(lǐng)導(dǎo)廠商賽靈思公司( Xilinx, Inc. (NASDAQ: XLNX) )今天宣布推出兩款XtremeDSP開發(fā)平臺:XtremeDSP視頻入門套件以及XtremeDSP DSP入門套件,分別用于低成本視頻開發(fā)和基于Spartan-3A DSP FPGA的DSP系統(tǒng)開發(fā)。這兩個開發(fā)平臺都基于Spartan?-3A DSP FPGA。 XtremeDSP視頻入門套件是為需要低

- 關(guān)鍵字: DSP

定點(diǎn)DSP C55X實(shí)現(xiàn)浮點(diǎn)相關(guān)運(yùn)算

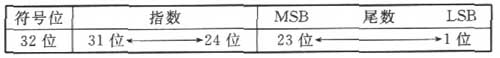

- 引 言 DSP結(jié)構(gòu)可以分為定點(diǎn)和浮點(diǎn)型兩種。其中,定點(diǎn)型DSP可以實(shí)現(xiàn)整數(shù)、小數(shù)和特定的指數(shù)運(yùn)算,它具有運(yùn)算速度快、占用資源少、成本低等特點(diǎn);靈活地使用定點(diǎn)型DSP進(jìn)行浮點(diǎn)運(yùn)算能夠提高運(yùn)算的效率。目前對定點(diǎn)DSP結(jié)構(gòu)支持下的浮點(diǎn)需求也在不斷增長,主要原因是:實(shí)現(xiàn)算法的代碼往往是采用C/C++編寫,如果其中有標(biāo)準(zhǔn)型的浮點(diǎn)數(shù)據(jù)處理,又必須采用定點(diǎn)DSP器件,那么就需要將浮點(diǎn)算法轉(zhuǎn)換成定點(diǎn)格式進(jìn)行運(yùn)算。同時,定點(diǎn)DSP結(jié)構(gòu)下的浮點(diǎn)運(yùn)算有很強(qiáng)的可行性,因?yàn)镃語言和匯編語言分別具有可移植性強(qiáng)和運(yùn)算效率高的

- 關(guān)鍵字: DSP

針對低成本視頻和DSP系統(tǒng)開發(fā)Xilinx再推兩款XtremeDSP開發(fā)平臺

- 賽靈思公司宣布推出兩款XtremeDSP開發(fā)平臺:XtremeDSP視頻入門套件以及XtremeDSP DSP入門套件,分別用于低成本視頻開發(fā)和基于Spartan-3A DSP FPGA的DSP系統(tǒng)開發(fā)。這兩個開發(fā)平臺都基于Spartan -3A DSP FPGA。 XtremeDSP視頻入門套件是為需要低成本和高性能視頻處理的視頻應(yīng)用而提供的完整開發(fā)平臺。這一新套件為視頻應(yīng)用開發(fā)人員提供了加快開發(fā)過程所需要的一切,包括強(qiáng)大的視頻專用IP、參考設(shè)計、XtremeDSP和賽靈思嵌入式處理開發(fā)工具,

- 關(guān)鍵字: 賽靈思 DSP

利用FPGA進(jìn)行高速可變周期脈沖發(fā)生器設(shè)計

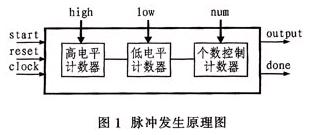

- 1 概括 要求改變脈沖周期和輸出脈沖個數(shù)的脈沖輸出電路模塊在許多工業(yè)領(lǐng)域都有運(yùn)用。采用數(shù)字器件設(shè)計周期和輸出個數(shù)可調(diào)節(jié)的脈沖發(fā)生模塊是方便可行的。為了使之具有高速、靈活的優(yōu)點(diǎn),本文采用atelra公司的可編程芯片F(xiàn)PGA設(shè)計了一款周期和輸出個數(shù)可變的脈沖發(fā)生器。經(jīng)過板級調(diào)試獲得良好的運(yùn)行效果。 2 總體設(shè)計思路 脈沖的周期由高電平持續(xù)時間與低電平持續(xù)時間共同構(gòu)成,為了改變周期,采用兩個計數(shù)器來分別控制高電平持續(xù)時間和低電平持續(xù)時間。計數(shù)器采用可并行加載初始值的n位減法計數(shù)器。設(shè)定:當(dāng)

- 關(guān)鍵字: FPGA

一種基于A/D和DSP的高速數(shù)據(jù)采集技術(shù)

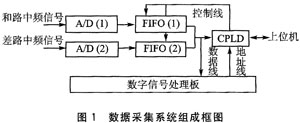

- 摘要 雷達(dá)接收機(jī)將雷達(dá)回波信號變成中頻信號,數(shù)字信號處理系統(tǒng)對中頻信號采樣和處理。本文介紹一種基于A/D和DSP的中頻信號采集技術(shù);給出數(shù)據(jù)采集系統(tǒng)的原理和框圖,并對A/D與DSP的接口電路進(jìn)行分析。用FIFO作為兩者之間的接口效果很好;DSP通過CPLD對采樣時序進(jìn)行控制,可增強(qiáng)系統(tǒng)的靈活性。 關(guān)鍵詞 A/D DSP 高速數(shù)據(jù)采集 FIFO 中頻信號分為和差兩路,高速A/D與DSP組成的數(shù)據(jù)采集系統(tǒng)要分別對這兩路信號進(jìn)行采集。對于兩路數(shù)據(jù)采集電路,A/D與DSP的接口連接是一樣的。兩個A

- 關(guān)鍵字: A/D DSP 高速數(shù)據(jù)采集 FIFO

增值服務(wù):FPGA分銷關(guān)鍵詞

- FPGA是現(xiàn)場可編程門陣列產(chǎn)品的簡稱。消費(fèi)電子等領(lǐng)域的迅猛發(fā)展,引起了FPGA廠商的重視,他們紛紛應(yīng)對發(fā)展推出了新的產(chǎn)品以滿足市場需要。Xilinx及時推出適應(yīng)新技術(shù)需要的Spartan-3A系列,Altera公司推出低功耗的CycloneIII系列產(chǎn)品,ACTEL公司推出了IGLOO系列。FPGA市場展開新一輪的競爭,各大FPGA廠商的分銷商都在配合原廠大力推廣新的產(chǎn)品。 FPGA分銷對技術(shù)支持要求高 FPGA產(chǎn)品的技術(shù)專業(yè)性較強(qiáng),它的分銷與ASIC(專用集成電路)、ASSP(特定應(yīng)用的

- 關(guān)鍵字: FPGA

一種基于A/D和DSP的高速數(shù)據(jù)采集技術(shù)

- 摘要 雷達(dá)接收機(jī)將雷達(dá)回波信號變成中頻信號,數(shù)字信號處理系統(tǒng)對中頻信號采樣和處理。本文介紹一種基于A/D和DSP的中頻信號采集技術(shù);給出數(shù)據(jù)采集系統(tǒng)的原理和框圖,并對A/D與DSP的接口電路進(jìn)行分析。用FIFO作為兩者之間的接口效果很好;DSP通過CPLD對采樣時序進(jìn)行控制,可增強(qiáng)系統(tǒng)的靈活性。 關(guān)鍵詞 A/D DSP 高速數(shù)據(jù)采集 FIFO 中頻信號分為和差兩路,高速A/D與DSP組成的數(shù)據(jù)采集系統(tǒng)要分別對這兩路信號進(jìn)行采集。對于兩路數(shù)據(jù)采集電路,A/D與DSP的接口連接是一樣的。兩個A

- 關(guān)鍵字: A/D DSP 高速數(shù)據(jù)采集 FIFO

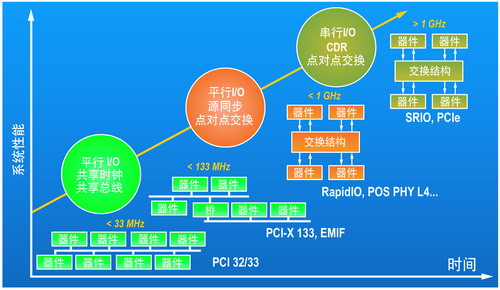

利用串行RapidIO連接功能增強(qiáng)DSP協(xié)處理能力

- 目前,對高速通信與超快計算的需求正與日俱增。有線和無線通信標(biāo)準(zhǔn)的應(yīng)用隨處可見,數(shù)據(jù)處理架構(gòu)每天都在擴(kuò)展。較為普遍的有線通信方式是以太網(wǎng)(LAN、WAN 和 MAN 網(wǎng)絡(luò))。手機(jī)通信是最為常見的無線通信方式,由應(yīng)用了 DSP 的架構(gòu)實(shí)現(xiàn)。電話作為語音連接的主要工具,目前正在不斷滿足日益增強(qiáng)的語音、視頻和數(shù)據(jù)要求。 系統(tǒng)設(shè)計人員在創(chuàng)建架構(gòu)時不僅需考慮三網(wǎng)合一模式這一高端需求,還需滿足以下要求:高性能;低延遲;較低的系統(tǒng)成本(包括 NRE);可擴(kuò)展、可延伸架構(gòu);集成現(xiàn)成 (OTS) 組件;分布式處理;

- 關(guān)鍵字: DSP

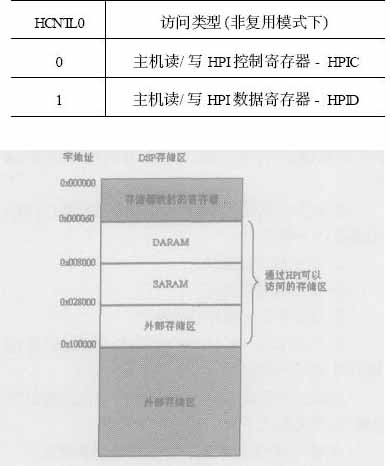

ARM CPU CS89712與C5510 DSP 的接口設(shè)計

- 摘 要:以Cirrus Logic公司的ARM 芯片和TI 公司的TMS320V DSP 為例,研究了ARM與DSP 的數(shù)據(jù)接——HPI 接口的相關(guān)技術(shù),并給出了在HPI 接口非復(fù)用模式下,CS89712 與C5510 的信號連接圖和嵌入式實(shí)時操作系統(tǒng)uCOS-II下驅(qū)動程序的部分關(guān)鍵源代碼。 關(guān)鍵詞:ARM CS89712;主機(jī)接口(HPI);TMS320VC5510 引 言 目前嵌入式系統(tǒng)已被廣泛地應(yīng)用到電子產(chǎn)品領(lǐng)域和無線通信、網(wǎng)絡(luò)通信等高端設(shè)備領(lǐng)域。32

- 關(guān)鍵字: ARM 接口 DSP 嵌入式 CPU

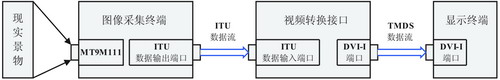

基于FPGA的數(shù)字視頻轉(zhuǎn)換接口的設(shè)計與實(shí)現(xiàn)

- 引言 本文從實(shí)際應(yīng)用的角度出發(fā),采用FPGA作為主控芯片,設(shè)計了一款數(shù)字視頻接口轉(zhuǎn)換設(shè)備,該設(shè)備針對于MT9M111這款數(shù)字圖像傳感器產(chǎn)生的ITU-R BT.656格式數(shù)據(jù)進(jìn)行采集、色彩空間變換、分辨率轉(zhuǎn)換等操作,完成了從ITU-R BT.656格式數(shù)據(jù)到DVI格式數(shù)據(jù)的轉(zhuǎn)換,使得MT9M111數(shù)字圖像傳感器的BT656數(shù)據(jù)格式圖像能夠以1280×960(60Hz)和1280×1024(60Hz)兩種顯示格式在DVI-I接口的顯示器上顯示,并且還具有圖像靜止功能,在系統(tǒng)空

- 關(guān)鍵字: FPGA 數(shù)字視頻 接口 傳感器

最新方法:怎樣提高DSP采樣精度

- 1 ,AD7858的主要特性 AD7858是AD公司推出的12位串口、高速、低功耗、逐次逼近式AD轉(zhuǎn)換器。它可在3~5.5 V的電壓下工作,其數(shù)據(jù)通過率高達(dá)200 kSPS。該芯片內(nèi)含一個低噪聲、寬頻帶的跟蹤/保持放大器,可以處理高達(dá)200 kHz的寬頻信號。 AD7858很容易與微處理器或DSP接口。輸入信號從CONVST的下降沿開始被采樣(此位可通過硬件引腳或軟件位操作),轉(zhuǎn)換也從此點(diǎn)啟動。忙信號線在轉(zhuǎn)換起始時為高電平,之后在400μs后跳變?yōu)榈碗娖揭员硎巨D(zhuǎn)換結(jié)束。

- 關(guān)鍵字: DSP 采樣 精度

基于FPGA的數(shù)字視頻轉(zhuǎn)換接口的設(shè)計與實(shí)現(xiàn)

- 引言 本文從實(shí)際應(yīng)用的角度出發(fā),采用FPGA作為主控芯片,設(shè)計了一款數(shù)字視頻接口轉(zhuǎn)換設(shè)備,該設(shè)備針對于MT9M111這款數(shù)字圖像傳感器產(chǎn)生的ITU-R BT.656格式數(shù)據(jù)進(jìn)行采集、色彩空間變換、分辨率轉(zhuǎn)換等操作,完成了從ITU-R BT.656格式數(shù)據(jù)到DVI格式數(shù)據(jù)的轉(zhuǎn)換,使得MT9M111數(shù)字圖像傳感器的BT656數(shù)據(jù)格式圖像能夠以1280×960(60Hz)和1280×1024(60Hz)兩種顯示格式在DVI-I接口的顯示器上顯示,并且還具有圖像靜止功能,在系統(tǒng)空

- 關(guān)鍵字: FPGA

USB2.0接口和DSP構(gòu)成的高速數(shù)據(jù)采集系統(tǒng)

- 摘要:介紹一個基于USB2.0接口和DSP的高速數(shù)據(jù)采集處理系統(tǒng)的工作原理、設(shè)計及實(shí)現(xiàn)。該高速數(shù)據(jù)采集處理系統(tǒng)采用TI公司的TMS320C6000數(shù)字信號處理器和Cypress公司的USB2.0接口芯片,可以實(shí)現(xiàn)高速采集和實(shí)時處理,有著廣泛 的應(yīng)用前景。 關(guān)鍵詞:USB2.0 CY7C68013 DSP 高速數(shù)據(jù)采集 隨著數(shù)字信號處理理論和計算機(jī)的不斷發(fā)展,現(xiàn)代工業(yè)生產(chǎn)和科學(xué)技術(shù)研究都需要借助于數(shù)字處理方法。進(jìn)行數(shù)字處理的先決條件是將所研究的對象進(jìn)行數(shù)字化,因此數(shù)據(jù)采集與處理技術(shù)日益得到重視

- 關(guān)鍵字: USB2.0 CY7C68013 DSP 高速數(shù)據(jù)采集

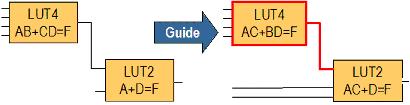

利用SmartCompile和賽靈思的設(shè)計工具進(jìn)行設(shè)計保存

- 在FPGA環(huán)境下,設(shè)計保存實(shí)施比較復(fù)雜,需要保存的事項(xiàng)包括:一項(xiàng)設(shè)計的HDL描述、一個模塊的綜合網(wǎng)表、約束文件內(nèi)的布局信息,以及在局部比特文件中的配置數(shù)據(jù)。賽靈思集成軟件環(huán)境(ISE) 9.1i 軟件以新的SmartCompile 技術(shù)為特色,其中包含兩種新的方法:SmartGuide和Partitions,這兩種方法可以保存像布局或布線這樣的設(shè)計執(zhí)行數(shù)據(jù),并且可以減少解決問題所花費(fèi)的時間。 SmartGuide采用命名和拓樸匹配技術(shù)來識別一個FPGA設(shè)計中相對于以前的實(shí)現(xiàn)還沒有發(fā)生改變的各個部

- 關(guān)鍵字: FPGA

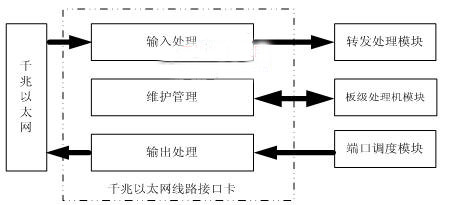

基于PM3388和FPGA的網(wǎng)絡(luò)接口設(shè)計

- 本文根據(jù)十接口千兆以太網(wǎng)線路接口卡設(shè)計的功能需求和性能需求,按照數(shù)據(jù)處理流程劃分功能模塊,以PM3388作為鏈路層處理芯片和兩片高性能FPGA作為鏈路層處理芯片完成了系統(tǒng)設(shè)計,并給出了具體實(shí)現(xiàn)方案。對兩片F(xiàn)PGA控制功能的實(shí)現(xiàn)做了重點(diǎn)闡述,對實(shí)現(xiàn)難點(diǎn)做了深入的分析。 1 前言 隨著網(wǎng)絡(luò)規(guī)模的持續(xù)膨脹和新型網(wǎng)絡(luò)應(yīng)用需求的不斷增長,目前基于IPv4技術(shù)的因特網(wǎng)在可擴(kuò)展性、IP地址空間、安全、服務(wù)質(zhì)量控制、移動性、運(yùn)營管理和盈利模式等諸多方面面臨著挑戰(zhàn),尤其是地址空間匱乏、可擴(kuò)展性差等缺陷嚴(yán)重制

- 關(guān)鍵字: FPGA

dsp+fpga介紹

您好,目前還沒有人創(chuàng)建詞條dsp+fpga!

歡迎您創(chuàng)建該詞條,闡述對dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司