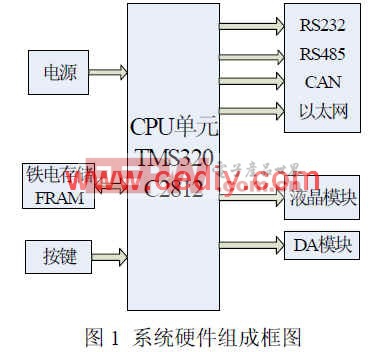

- 本文基于電力電子裝置的實際工程調試需要設計出了一款帶液晶顯示的通用控制器。該控制器采用 TMS320C2812作為為控制芯片,使用中文液晶菜單進行操作。控制器通過菜單設定對相關設備的控制命令,同時對接收到的電參數進行實時顯示。另外,控制器還可以通過 DA接口將接收到的數字電量轉換為模擬量方便使用示波器進行實時波形顯示。該控制器支持 RS232、RS485、CAN通訊和以太網通訊協議,通訊方式靈活,便于各種設備的調試。

- 關鍵字:

控制器 設計 通用 液晶顯示 DSP 基于 通信協議

- 隨著DSP技術的進步,計算能力更強、功耗更低和體積更小的DSP已經出現,使3G手機上植入更精確更復雜的自動語...

- 關鍵字:

手機 語音識別 DSP 應用 3G

- 摘要:電壓、電流、溫度等模擬量的監測在工業生活中都有很廣泛的應用,通過監測到的數據,可以對其進行及時調整,為人們的生產生活帶來了便利與保證。系統主電路采用Actel公司提供的Fusion系列FPGA,用以實現溫度控制

- 關鍵字:

FPGA 數字顯示 測控系統

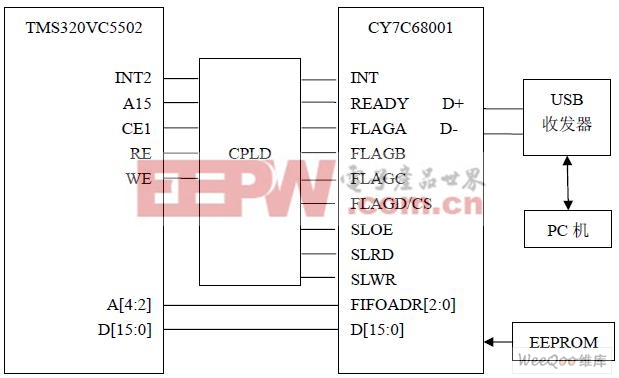

- 論述了基于 USB的 DSP核信號數據采集系統通訊接口的設計方法,其中數據采集系統中的 USB通訊芯片采用 CY7C68001,上位機通訊界面采用 Microsoft Visual C++編寫,同時采用 CPLD很好地解決了各芯片的邏輯問題。實際測試表明利用 USB接口提高了數據傳輸的速率,節省了資源,而且即插即用的方式方便了連接。

- 關鍵字:

接口 設計 通訊 系統 信號 采集 DSP 數字信號

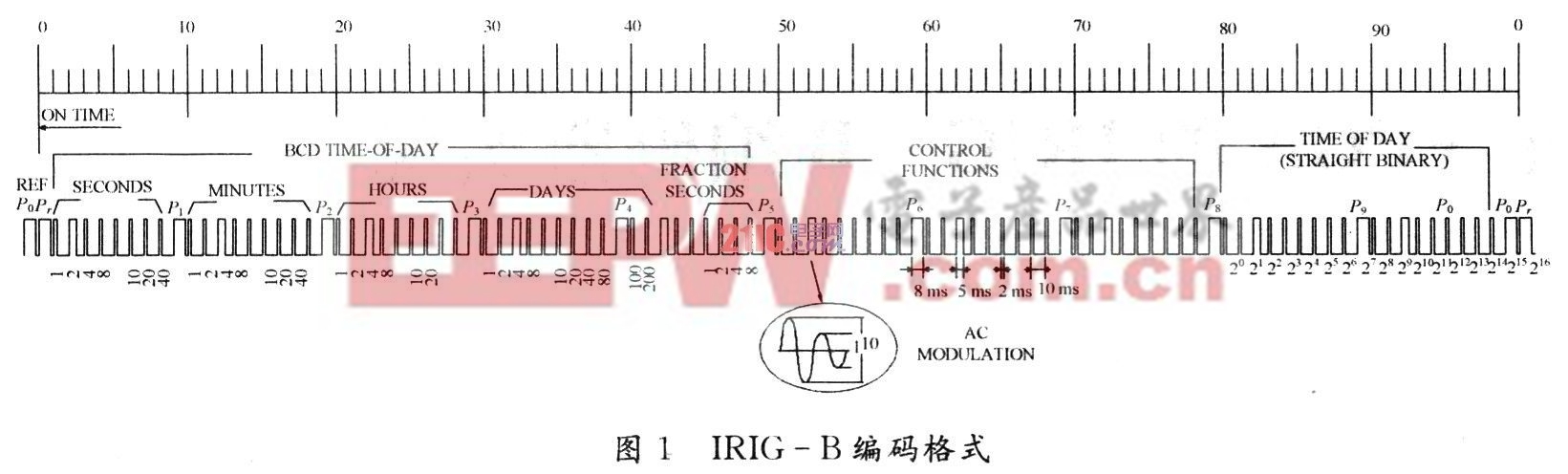

- 摘要:旨在設計一款基于FPGA的IRIG-B時間系統。該系統采用FPGA作為控制器,GPS引擎M12T作為標準時鐘源,利用M12T輸出的100 pps信號觸發IRIG-B編碼模塊,完成DC碼編碼。在DC碼的基礎上,通過正弦查找表實現了IRIG-B交

- 關鍵字:

實現 編碼器 IRIG-B FPGA 基于 FPGA

- 車牌識別模塊是車牌識別(LPR)系統的核心。論文根據國內汽車牌照的特點,對車牌識別模塊中的預處理、字符分割及字符識別技術提出了改進的算法,并基于 DSP實現了對車牌純字符區域的準確提取、分割。改進點有采用對邊緣銳化后的二值圖像進行局部投影去除車牌背景、對各字符的外部輪廓進行統計特征提取以及充分利用數字“1”自身的特點設計識別方案。通過Code Composer Studio (CCS)對 358副車牌圖像進行了仿真測試,識別率為99.16%。

- 關鍵字:

DSP 圖像處理 車牌識別 中的應用

- 本文對多路測量信號的擴頻傳輸系統進行了研究,提出了對所傳輸信號的頻譜進行擴展并利用碼分復用實現多路信號的復用傳輸的方法。分析了多路測量信號擴頻傳輸系統的 DSP系統實現的整體方案,并實現電路的設計。

- 關鍵字:

DSP 多路 測量信號 傳輸

- 隨著現代電子技術的發展,接口技術在設計中占據越來越重要的地位。多串口動態擴展通信技術在現場工業控制、智能家居等領域應用越來越廣泛。在當前的多串口的擴展應用中,雖然市面上有部分的多串口擴展芯片,但是其可擴展的串口數量有限并且擴展的個數是固定的,而且這些擴展芯片普片存在著價格比較昂貴、芯片體積較大在電路板中占據很大的空間,功耗過高等問題。

基于Actel FPGA的多串口擴展設計采用了Actel公司高集成度,小體積,低功耗,低系統成本,高安全性和可靠性的小容量FPGA-A3P030進行設計,把若干接

- 關鍵字:

Actel FPGA 多串口 201003

- 對于許多半導體原廠來說,技術研討會是其推廣自身產品技術一個重要的市場手段,而對于授權分銷商來說,舉辦技術研討會似乎顯得有些“不務正業”之嫌。其實并非如此,對于半導體原廠和分銷商來說,舉辦技術研討會有各自的優勢,兩者如果能夠有效配合,甚至可以發揮出“1+1>2”的效果。

以安富利電子(Avnet)與賽靈思攜手舉辦的X-Fest 2010系列研討會為例,北京站會議實際到場工程師接近600人。據負責此項目的安富利亞太區技術經理曹鍵華介紹,X-fes

- 關鍵字:

Avnet DSP 電源 存儲接口 201003

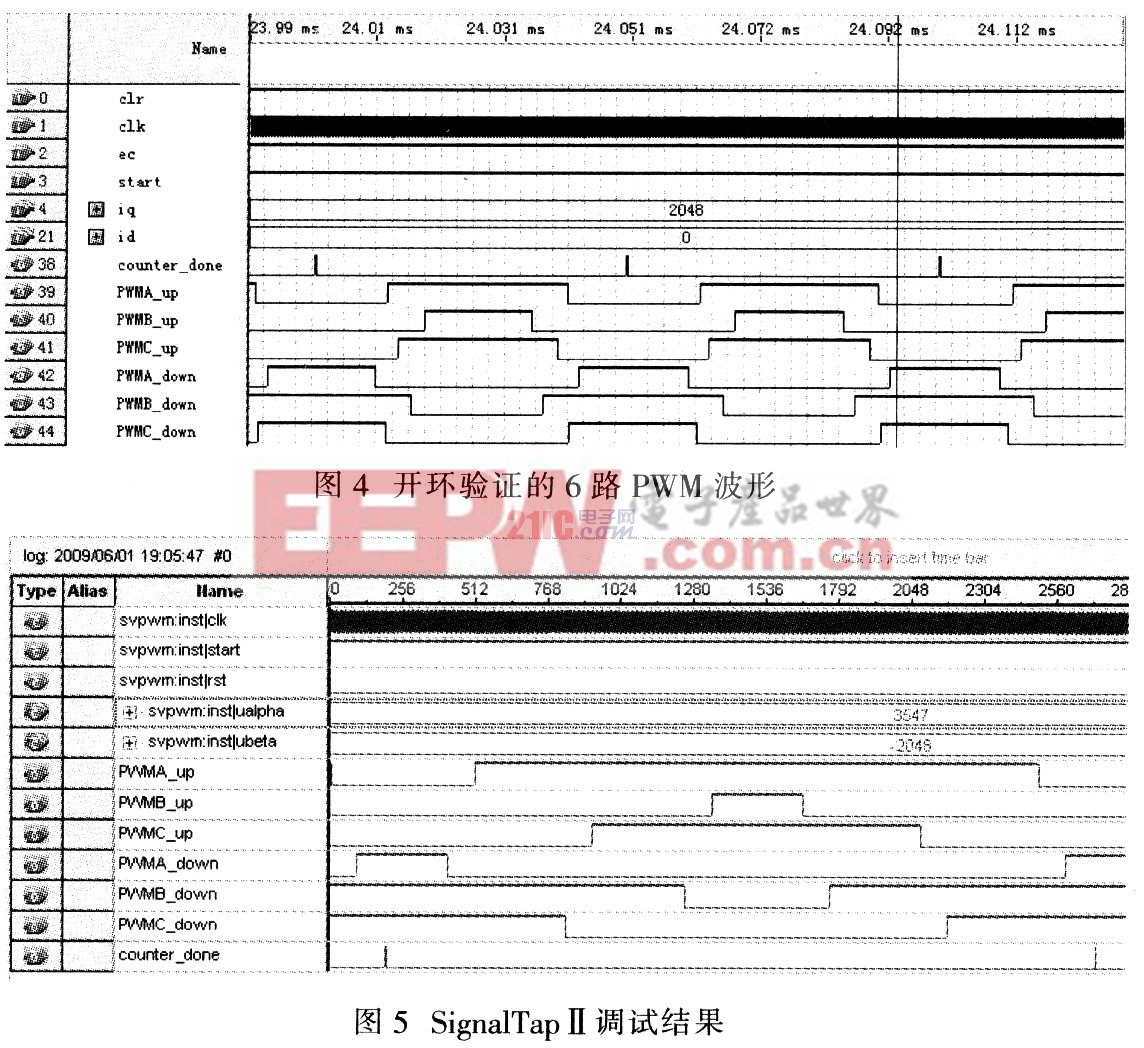

- 摘要:提出一種基于FPGA的永磁同步電機控制器的設計方案,該設計可應用于具有高動態性能要求的永磁同步電機伺服控制系統。為提高伺服控制系統的實時性,簡化電路及節省成本,該系統設計采用Ahera公司生產的CycloneII

- 關鍵字:

FPGA 永磁同步電機 制器設計 PMSM

- 摘要:為能充分利用數字技術可靠性高、靈活性強等優點,將自動增益控制AGC引入數字域,并針對超聲波氣體流量計中接收信號的特點,給出一種基于EPlK30TCl44-3的全數字AGC設計方案。測試結果表明該系統設計可以實現40

- 關鍵字:

FPGA AGC 超聲波 氣體流量計

- 摘要:HDB3(三階高密度雙極性)碼具有無直流分量、低頻成分少、連零個數不超過3個、便于提取時鐘信號等特點。通過對HDB3編解碼原理進行分析和研究,提出一種基于FPGA的HDB3編解碼實現方法,給出Verilog HDL語言的實現

- 關鍵字:

FPGA HDB3 編解碼

dsp+fpga介紹

您好,目前還沒有人創建詞條dsp+fpga!

歡迎您創建該詞條,闡述對dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473