- 基于DSP+MCU的列車滾動軸承故障診斷系統充分利用了DSP和MCU的信號處理和控制能力,提高了系統的數據處理效率。實驗結果表明,該系統通過Hilbert變換法提取出包絡信號,利用小波奇異性檢測進行故障診斷,取得了很好的效果。

- 關鍵字:

診斷 系統 設計 應用 故障 軸承 DSP MCU 列車 滾動 基于

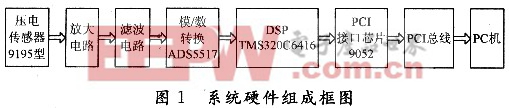

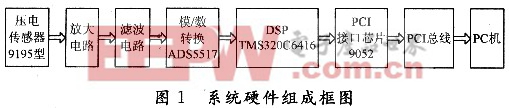

- 基于DSP的動態稱重系統設計,通過分析目前國內外使用的動態稱重系統(WIM)存在的問題,選擇石英壓電稱重傳感器作為動態稱重傳感器,并采用TMS320C6416的DSP核心器件設計并實現了相應的動態稱重系統,利用Delphi完成了該動態稱重系統的軟件設計。該系統克服了傳統動態稱重系統測量精度低、所需時間長等缺點,通過實測表明該系統運行良好,應用前景廣泛。

- 關鍵字:

系統 設計 稱重 動態 DSP 基于

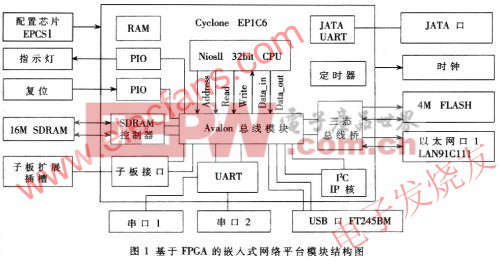

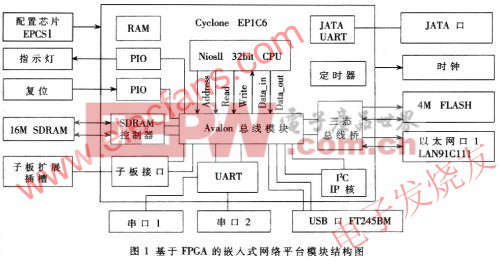

- 基于FPGA的片上系統和嵌入式系統的遠程監控系統,本系統立足于利用Intemet實現核環境信息的遠程采集。在實現上,采用了基于SOPC技術的嵌入式解決方案,通過在FPGA中嵌入NioslI軟核處理器和所需外設的IP Core(硅知識產權核),然后再配備相應的網絡接口,實現利用互聯

- 關鍵字:

系統 監控系統 遠程 嵌入式 基于 FPGA

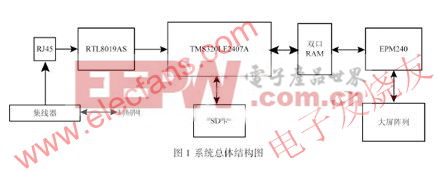

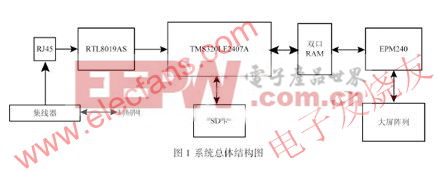

- 基于DSP的LED大屏幕顯示系統,目前采用的LED大屏幕顯示系統的控制電路,大多由單個或多個CPU及復雜的外圍電路組成,這種電路設計,單片機編程比較復雜,整個電路的調試比較麻煩,可靠性和實時性很難得到保證。針對這種情況,提出一種SD卡存儲顯示

- 關鍵字:

顯示系統 大屏幕 LED DSP 基于

- 本系統立足于利用Intemet實現核環境信息的遠程采集。在實現上,采用了基于SOPC技術的嵌入式解決方案,通過...

- 關鍵字:

遠程監控 SoC 嵌入式 FPGA

- 一個網絡的頻率特性包括幅頻特性和相頻特性,在系統設計時,各個網絡的頻率特性對該系統的穩定性、工作頻帶...

- 關鍵字:

掃頻儀 FPGA 單片機 掃頻信號

- 電子產品世界,為電子工程師提供全面的電子產品信息和行業解決方案,是電子工程師的技術中心和交流中心,是電子產品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網絡家園

- 關鍵字:

65nm TD-SCDMA FPGA 多模無線基站

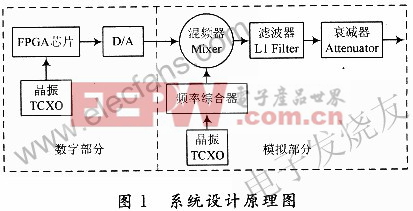

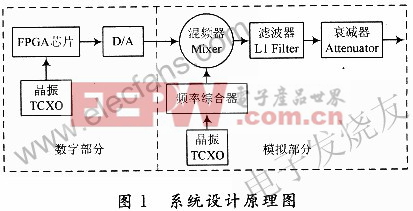

- 基于FPGA芯片和頻率合成器ADF4360-4的GPS信號源的設計方案, 頻率合成器是發射系統和接收系統中的核心器件,采用相位負反饋頻率控制技術,具有良好的窄帶載波跟蹤性能和帶寬調制跟蹤性能,為系統上、下變頻提供本振信號,對相位噪聲和雜散具有很好的抑制作用,通過鎖相頻率合

- 關鍵字:

GPS 信號源 設計 方案 ADF4360-4 合成器 FPGA 芯片 頻率

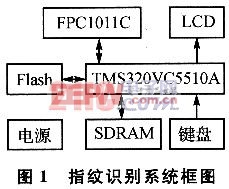

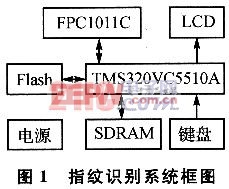

- 摘要:闡述一款基于DSP(Digital Signal Processor)的嵌入式指紋識別系統,對其硬件設計電路和軟件設計進行了詳細的論述。設計了雙電源切換系統,通過SPI協議與指紋采集頭FPC1011C和液晶屏進行通信,能夠方便地進行指

- 關鍵字:

DSP 傳感器 電源

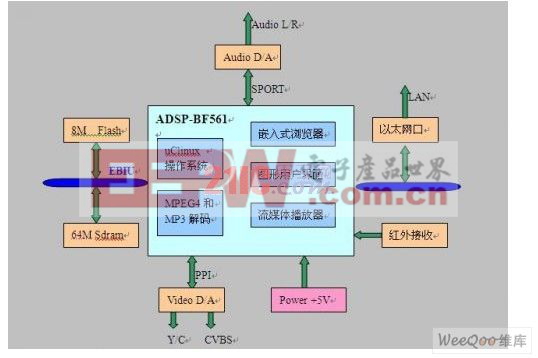

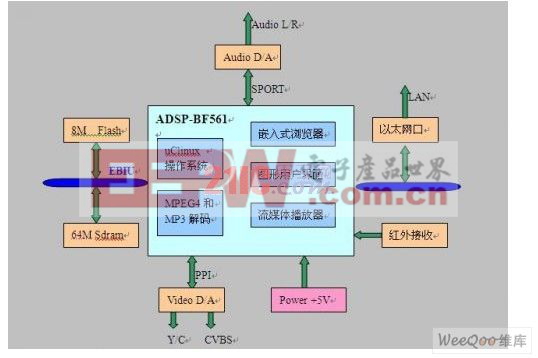

- 基于DSP的寬帶信息終端設計與實現, 摘要:本文研究并實現了一種基于DSP的寬帶信息終端,該系統采用ADI公司Blackfin系列ADSP-BF561處理器作為系統核心。文章介紹了系統設計和軟件設計,并給出了經市場驗證的實踐結論。 1 引言 隨著家電、通信、

- 關鍵字:

DSP

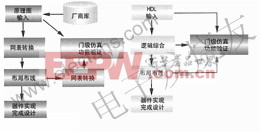

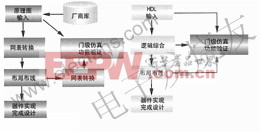

- FPGA/EPLD的自上而下設計方法,FPGA/EPLD的自上而下(Top-Down)設計方法: 傳統的設計手段是采用原理圖輸入的方式進行的,如圖1所示。通過調用FPGA/EPLD廠商所提供的相應物理元件庫,在電路原理圖中繪制所設計的系統,然后通過網表轉換產生某一特

- 關鍵字:

方法 設計 自上而下 FPGA/EPLD

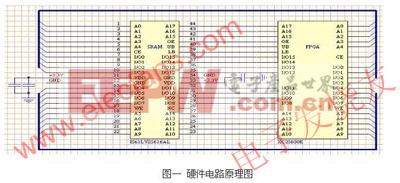

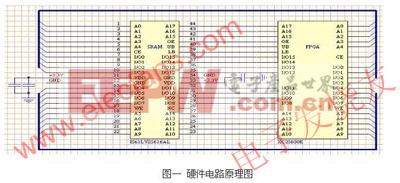

- 基于FPGA與SRAM的大容量數據存儲的設計, 1 前言 針對FPGA中內部BlockRAM有限的缺點,提出了將FPGA與外部SRAM相結合來改進設計的方法,并給出了部分VHDL程序。 2 硬件設計 這里將主要討論以Xilinx公司的FPGA(XC2S600E-6fg456)和ISSI公司的SRAM(IS61

- 關鍵字:

存儲 設計 數據 大容量 FPGA SRAM 基于

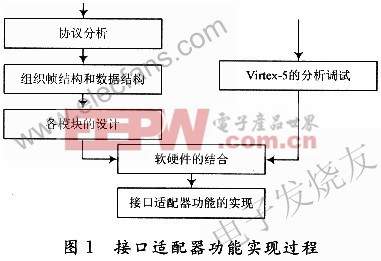

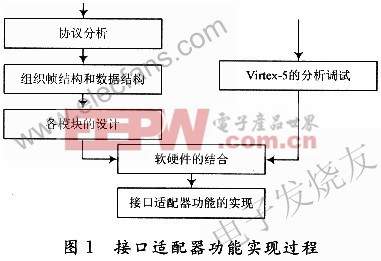

- 基于上位機與FPGA開發板的光纖通道接口適配器, 隨著存儲技術的迅速發展,存儲容量得到了迅速的增長,存儲系統的數據傳輸速度成為了主要的瓶頸。光纖的傳輸具有其速度上的優勢,然而,在光纖傳輸要受到光纖通道接口的限制,因此光纖通道應用于高速數據傳輸的一

- 關鍵字:

通道 接口 適配器 光纖 開發 上位 FPGA 基于

- 摘要:針對現有電網實時監測錄波系統的缺陷,設計出一種結合DSP與Labwindows/CVI軟件的故障錄波器。分析了FFT精確快速分析諧波的能力及其在DSP上的實現方法。介紹了硬件結構原理,給出硬件設計框圖和LabWindows/CV

- 關鍵字:

LabWindows DSP CVI 電力故障

dsp+fpga介紹

您好,目前還沒有人創建詞條dsp+fpga!

歡迎您創建該詞條,闡述對dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473