隨著數(shù)字技術(shù)的飛速發(fā)展,各種數(shù)字顯示屏也隨即涌現(xiàn)出來有LED、LCD、DLP等,各種數(shù)字大屏幕的控制系統(tǒng)多種多樣,...

關(guān)鍵字:

FPGA 芯片控制 LED

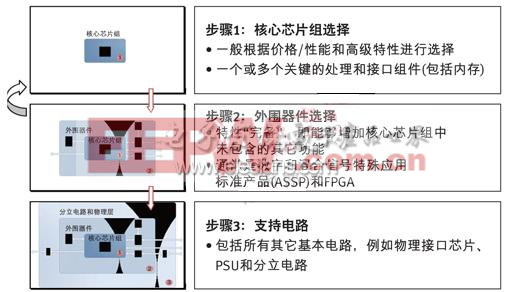

FPGA平臺架構(gòu)提升信息娛樂系統(tǒng)設(shè)計靈活性,開發(fā)車載信息娛樂系統(tǒng)面臨著前所未有的挑戰(zhàn)。事實上,支持眾多不一致甚至矛盾的要求需要采用全新的思路。設(shè)計基于FPGA的平臺就是一種可行的解決方案,可通過設(shè)計靈活性來滿足多樣化的汽車要求。 對于那些想要達到

關(guān)鍵字:

系統(tǒng) 設(shè)計 靈活性 娛樂 信息 平臺 架構(gòu) 提升 FPGA

基于DSP的電子浮標(biāo)設(shè)計方案,電子浮標(biāo)由于沒有本艦噪聲的影響,對水下目標(biāo)的探測靈敏度高;此外它可通過飛機布放和回收,具有搜索面積大、偵察效率高、使用方便等優(yōu)點,已成為偵察、反潛領(lǐng)域的重要裝備。而將多個浮標(biāo)組成網(wǎng)絡(luò),就可對大范圍海域進

關(guān)鍵字:

設(shè)計 方案 浮標(biāo) 電子 DSP 基于

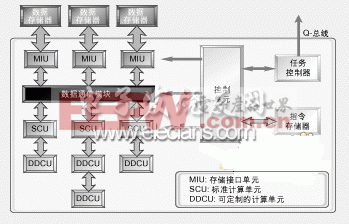

高性能定點DSP位處理單元BMU的設(shè)計,1 功能概述

關(guān)鍵字:

BMU 設(shè)計 單元 處理 定點 DSP 高性能

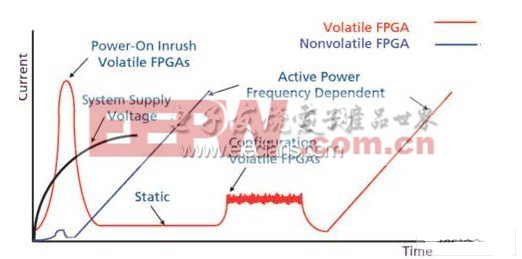

FPGA設(shè)計當(dāng)中的功耗問題研究,隨著FPGA的密度越來越高,設(shè)計者們正在節(jié)能降耗方面取得越來越多的進展。出現(xiàn)降低功耗這一趨勢的另一個原因是FPGA正在越來越廣泛地應(yīng)用于智能手機、媒體播放器、游戲機、衛(wèi)星導(dǎo)航設(shè)備以及數(shù)碼相機/攝像機等便攜式設(shè)備

關(guān)鍵字:

問題 研究 功耗 當(dāng)中 設(shè)計 FPGA

全球領(lǐng)先的硅產(chǎn)品知識產(chǎn)權(quán)(SIP)平臺解決方案和數(shù)字信號處理器(DSP)內(nèi)核授權(quán)廠商CEVA公司宣布成為半導(dǎo)體行業(yè)首家提供經(jīng)Dolby認證的Dolby Mobile DSP內(nèi)核實施方案的企業(yè)。以高性能CEVA-TeakLite-III DSP為基礎(chǔ),CEVA的第三代Dolby Mobile技術(shù)實施方案包括用于移動產(chǎn)品的Dolby Digital Plus支持,對于采納Dolby最新移動音頻增強特性而進行設(shè)計的移動音頻處理器客戶,可提供顯著的上市時間和功耗節(jié)省優(yōu)勢。

關(guān)鍵字:

CEVA Dolby Mobile DSP

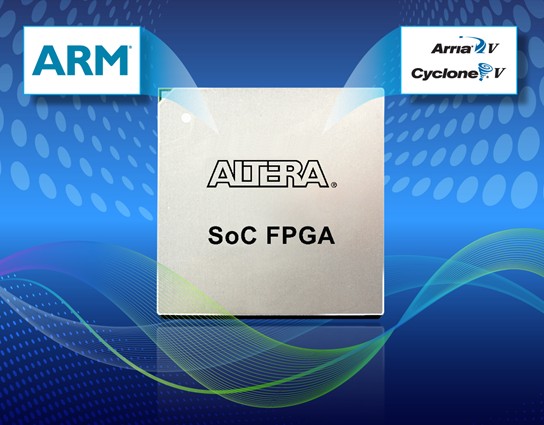

Altera公司2011年10月12號宣布可以提供FPGA業(yè)界的第一個虛擬目標(biāo)平臺,支持面向Altera最新發(fā)布的SoC FPGA器件立即開始器件專用嵌入式軟件的開發(fā)。在Synopsys有限公司成熟的虛擬原型開發(fā)解決方案基礎(chǔ)上,SoC FPGA虛擬目標(biāo)是基于PC在Altera SoC FPGA開發(fā)電路板上的功能仿真。

關(guān)鍵字:

Altera 嵌入式 SoC FPGA

Altera公司2011年12日發(fā)布其基于ARM的SoC FPGA系列產(chǎn)品,在單芯片中集成了28-nm Cyclone V和Arria V FPGA架構(gòu)、雙核ARM Cortex-A9 MPCore處理器、糾錯碼(ECC)保護存儲器控制器、外設(shè)和寬帶互聯(lián)等。這些SoC FPGA繼承了ARM豐富的軟件開發(fā)工具、調(diào)試器、操作系統(tǒng)、中間件和應(yīng)用程序等輔助系統(tǒng)功能。

關(guān)鍵字:

Altera 嵌入式 SoC FPGA

摘要:在現(xiàn)代伺服系統(tǒng)中,位置檢測和轉(zhuǎn)速測量技術(shù)是提高控制系統(tǒng)精度的關(guān)鍵技術(shù)。本文詳細的介紹了使用光電編碼...

關(guān)鍵字:

DSP OEP電路 光電編碼器 MT法測速

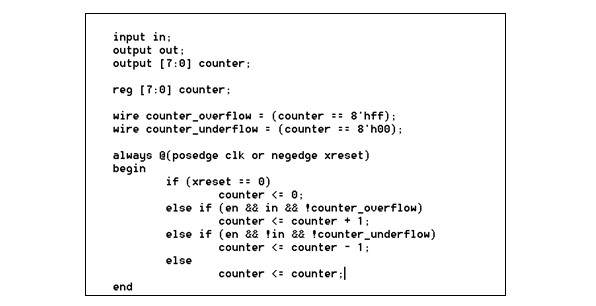

[Dave坐在實驗室中,凝視著充滿Verilog代碼的屏幕……]

T:你好Dave,現(xiàn)在你在做什么?!

D:噢,你好T博士,這是一個新的芯片的印刷電路板(PCB)原型,它是一個混合信號芯片。我們正在構(gòu)建一個FPGA的數(shù)字部分。FPGA的Verilog代碼看起來是這樣的。(Dave手指著屏幕。)

關(guān)鍵字:

Intersil FPGA

2011年10月12號,北京——Altera公司(Nasdaq:ALTR)今天宣布可以提供FPGA業(yè)界的第一個虛擬目標(biāo)平臺,支持面向Al...

關(guān)鍵字:

Altera SoC FPGA 虛擬目標(biāo)

加利福尼亞州圣克拉拉市2011年10月11日訊–Tensilica今日宣布,全球領(lǐng)先的DSP(數(shù)字信號處理)軟件解決方案供應(yīng)...

關(guān)鍵字:

DSP Tensilica

引 言 在電氣智能化發(fā)展無處不在的今天, 無數(shù)用電場合離不開逆變電源系統(tǒng)( Inverted Pow er Supply System,IPS) 為現(xiàn)場設(shè)備提供穩(wěn)定的高質(zhì)量電源, 特別在如通信機房、服務(wù)器工作站、交通樞紐調(diào)度中心、醫(yī)院、

關(guān)鍵字:

設(shè)計 逆變電源 DSP ARM7 基于

2011年10月11日訊 –Tensilica今日宣布,全球領(lǐng)先的DSP(數(shù)字信號處理)軟件解決方案供應(yīng)商IntegrIT的NatureDSP數(shù)學(xué)庫,目前可用于Tensilica ConnX BBE16基帶DSP的片上系統(tǒng)(SOC)設(shè)計。

關(guān)鍵字:

Tensilica DSP

定制DSP設(shè)計MPEG-4無線視頻產(chǎn)品,MPEG-4這種視頻標(biāo)準(zhǔn)對處理器的要求非常高。在整個移動通信結(jié)構(gòu)中,僅MPEG-4處理器這一部分就會毫不客氣地吞掉大量的資源。因而要想真正實現(xiàn)無線視頻應(yīng)用這一夢想,首先就必須解決MPEG-4信號處理問題。 工程師們已

關(guān)鍵字:

無線 視頻產(chǎn)品 MPEG-4 設(shè)計 DSP 定制

dsp+fpga介紹

您好,目前還沒有人創(chuàng)建詞條dsp+fpga!

歡迎您創(chuàng)建該詞條,闡述對dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。

創(chuàng)建詞條

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473