EEPW首頁(yè) >>

主題列表 >>

cpld/fpga

cpld/fpga 文章 最新資訊

基于CPLD的計(jì)算機(jī)并口EPP模式通訊實(shí)現(xiàn)

- 前言 計(jì)算機(jī)的并行接口一開(kāi)始是作為打印機(jī)接口而設(shè)計(jì)的。隨著計(jì)算機(jī)周邊設(shè)備的不斷擴(kuò)展,人們對(duì)提高計(jì)算機(jī)外設(shè)的數(shù)據(jù)采集速度的要求也越來(lái)越高。傳統(tǒng)的異步串行通訊方式雖然具有數(shù)據(jù)傳輸距離較遠(yuǎn)的優(yōu)勢(shì),但是由于數(shù)據(jù)

- 關(guān)鍵字: CPLD EPP 計(jì)算機(jī)并口 模式

CPLD在IGBT驅(qū)動(dòng)設(shè)計(jì)中的應(yīng)用

- 隨著國(guó)民經(jīng)濟(jì)的不斷發(fā)展,變頻調(diào)速裝置的應(yīng)用越來(lái)越廣泛。如何打破國(guó)外產(chǎn)品的壟斷,已成為一個(gè)嚴(yán)肅的課題擺在我國(guó)工程技術(shù)人員的面前。

在某型號(hào)大功率變頻調(diào)速裝置中,由于裝置的尺寸較大,考慮到結(jié)構(gòu) - 關(guān)鍵字: CPLD IGBT 驅(qū)動(dòng)設(shè)計(jì) 中的應(yīng)用

如何發(fā)現(xiàn)并解決FPGA設(shè)計(jì)中的時(shí)序問(wèn)題

- 耗費(fèi)數(shù)月精力做出的設(shè)計(jì)卻無(wú)法滿足時(shí)序要求,這確實(shí)非常令人傷心。然而,試圖正確地對(duì)設(shè)計(jì)進(jìn)行約束以保證滿足時(shí)序要求的過(guò)程幾乎同樣令人費(fèi)神。找到并確定時(shí)序約束本身通常也是非常令人頭痛的問(wèn)題。時(shí)序問(wèn)題的惱人之

- 關(guān)鍵字: FPGA 發(fā)現(xiàn) 時(shí)序

PCB版圖設(shè)計(jì)DD基于高速FPGA的PCB設(shè)計(jì)技術(shù)

- 如果高速PCB設(shè)計(jì)能夠像連接原理圖節(jié)點(diǎn)那樣簡(jiǎn)單,以及像在計(jì)算機(jī)顯示器上所看到的那樣優(yōu)美的話,那將是一件多么美好的事情。然而,除非設(shè)計(jì)師初入PCB設(shè)計(jì),或者是極度的幸運(yùn),實(shí)際的PCB設(shè)計(jì)通常不像他們所從事的電路設(shè)

- 關(guān)鍵字: PCB FPGA 版圖設(shè)計(jì) 設(shè)計(jì)技術(shù)

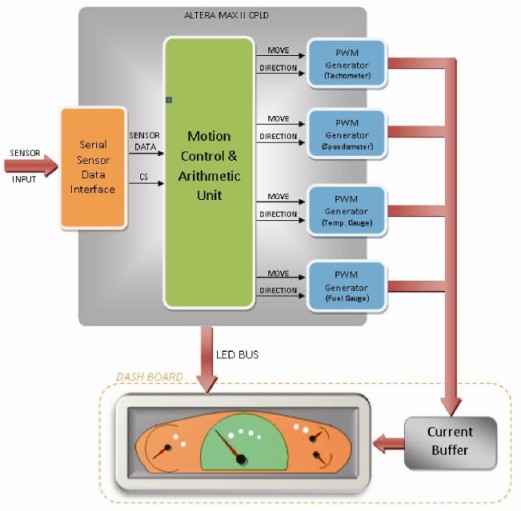

一種靈活的現(xiàn)代CPLD汽車數(shù)字儀表板設(shè)計(jì)

- ??????? 汽車儀表板成為匯集車輛安全和管理所有信息的神經(jīng)中樞,為駕駛員顯示各種信息。在當(dāng)今的數(shù)字時(shí)代車輛儀表系統(tǒng)必須能夠監(jiān)控所有關(guān)鍵功能,該系統(tǒng)甚至是個(gè)性化的。業(yè)界需求發(fā)展導(dǎo)致出現(xiàn)了很多半導(dǎo)體解決方案,從ASSP到全定制器件等。這些方案可能都是功能固定的解決方案,不能靈活地進(jìn)行產(chǎn)品開(kāi)發(fā),無(wú)法滿足設(shè)計(jì)人員的要求。作為對(duì)比,可更新解決方案在一條車輛產(chǎn)品線上支持多種相似的應(yīng)用,沒(méi)有任何多余的成本開(kāi)銷。這類定制解決方案以很低的成本滿足了所

- 關(guān)鍵字: CPLD 汽車數(shù)字儀表板 ADS

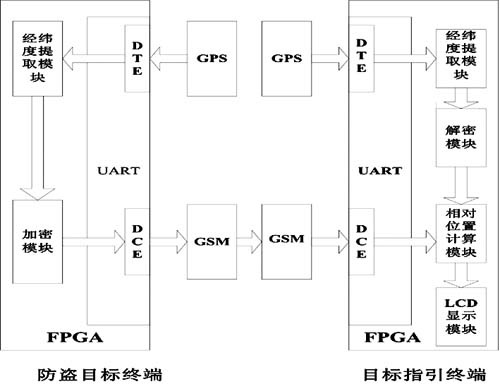

基于FPGA的防盜定位追蹤系統(tǒng)(08-100)

- 雖然現(xiàn)在市面上有很多類似的基于GPS的防盜系統(tǒng),但并不能很好地實(shí)現(xiàn)防盜和丟失后找回功能。本作品利用Spartan-3E開(kāi)發(fā)板彌補(bǔ)了以上缺陷。系統(tǒng)由防盜目標(biāo)終端和尋找指引終端組成。兩終端均基于FPGA設(shè)計(jì)實(shí)現(xiàn)。當(dāng)裝有防盜目標(biāo)終端的物品丟失后,防盜目標(biāo)終端將其所在經(jīng)緯度位置信息加密并發(fā)送給尋找指引終端,指引終端解密該信息并計(jì)算出與目標(biāo)終端的相對(duì)位置并通知用戶,從而最大限度地幫助人們找回丟失的物品的同時(shí)也保證了傳送信息的安全。

- 關(guān)鍵字: GSM FPGA 定位追蹤

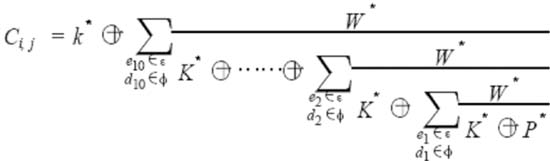

高可靠FPGA通信系統(tǒng)(08-100)

- 本作品主要目的在于針對(duì)ZigBee無(wú)線傳感器網(wǎng)絡(luò)中中心節(jié)點(diǎn)到控制中心的信息通信過(guò)程中存在的信息泄露和安全隱患,自行設(shè)計(jì)一套可移動(dòng)基于FPGA平臺(tái)的高可靠通信系統(tǒng)。在獨(dú)立開(kāi)發(fā)的基于CC2430芯片的無(wú)線傳感器星型網(wǎng)絡(luò)中,無(wú)線網(wǎng)絡(luò)節(jié)點(diǎn)與Spartan平臺(tái)進(jìn)行信息交互,其中端到端的數(shù)據(jù)傳輸均實(shí)現(xiàn)AES加密。中心節(jié)點(diǎn)的服務(wù)器對(duì)有線網(wǎng)絡(luò)進(jìn)行實(shí)時(shí)安全監(jiān)測(cè),當(dāng)網(wǎng)絡(luò)中存在危險(xiǎn)情況時(shí)通過(guò)GSM報(bào)警,由此實(shí)現(xiàn)了高可靠的網(wǎng)絡(luò)通信保障環(huán)境。

- 關(guān)鍵字: ZigBee FPGA 加密

高可靠FPGA通信系統(tǒng)

- 1 系統(tǒng)設(shè)計(jì) 在工業(yè)控制領(lǐng)域,利用ZigBee和傳感器網(wǎng)絡(luò),使得數(shù)據(jù)的自動(dòng)采集、分析和處理變得更加容易,作為決策輔助系統(tǒng)的重要組成部分,ZigBee無(wú)線傳感器網(wǎng)絡(luò)在無(wú)線數(shù)據(jù)采集及監(jiān)控等領(lǐng)域得到了廣泛應(yīng)用。無(wú)線傳感

- 關(guān)鍵字: FPGA 通信系統(tǒng)

基于DSP+CPLD的交流電機(jī)調(diào)速系統(tǒng)的應(yīng)用

- 1 引言 生化反應(yīng)池在水處理過(guò)程中非常重要。需要通過(guò)調(diào)整風(fēng)機(jī)的轉(zhuǎn)速控制反應(yīng)池中的DO值。理論上應(yīng)該通過(guò)調(diào)節(jié)電動(dòng)機(jī)的轉(zhuǎn)速來(lái)實(shí)現(xiàn),但實(shí)際上卻是利用擋板閥門后者放空的方法進(jìn)行調(diào)節(jié)。這種方法極大地浪費(fèi)了電力資源。以

- 關(guān)鍵字: CPLD DSP 交流電機(jī) 調(diào)速系統(tǒng)

基于單片機(jī)和CPLD的高精度數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

- 1 引言數(shù)據(jù)采集系統(tǒng)的任務(wù),就是采集傳感器輸出的模擬信號(hào)轉(zhuǎn)換成計(jì)算機(jī)能識(shí)別的數(shù)字信號(hào),送入計(jì)算機(jī),將計(jì)算機(jī)得到的數(shù)據(jù)進(jìn)行顯示或打印,以便實(shí)現(xiàn)對(duì)某些物理量的監(jiān)視,其中一部分?jǐn)?shù)據(jù)還將被生產(chǎn)過(guò)程中的計(jì)算機(jī)控制

- 關(guān)鍵字: CPLD 單片機(jī) 高精度 數(shù)據(jù)采集

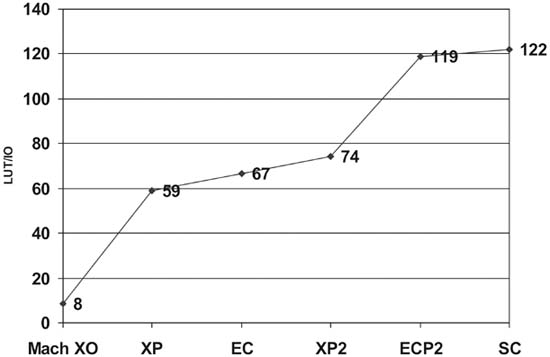

用內(nèi)部邏輯分析儀調(diào)試FPGA(08-100)

- 進(jìn)行硬件設(shè)計(jì)的功能調(diào)試時(shí),F(xiàn)PGA的再編程能力是關(guān)鍵的優(yōu)點(diǎn)。CPLD和FPGA早期使用時(shí),如果發(fā)現(xiàn)設(shè)計(jì)不能正常工作,工程師就使用“調(diào)試鉤”的方法。先將要觀察的FPGA內(nèi)部信號(hào)引到引腳,然后用外部的邏輯分析儀捕獲數(shù)據(jù)。然而當(dāng)設(shè)計(jì)的復(fù)雜程度增加時(shí),這個(gè)方法就不再適合了,其中有幾個(gè)原因。第一是由于FPGA的功能增加了,而器件的引腳數(shù)目卻緩慢地增長(zhǎng)。因此,可用邏輯對(duì)I/O的比率減小了,參見(jiàn)圖1。此外,設(shè)計(jì)很復(fù)雜時(shí),通常完成設(shè)計(jì)后只有幾個(gè)空余的引腳,或者根本就沒(méi)有空余的引腳能用于調(diào)試。

- 關(guān)鍵字: 萊迪思 FPGA 邏輯分析儀

提升創(chuàng)造力的數(shù)字設(shè)計(jì)工具:FPGA Editor(08-100)

- 工程師在設(shè)計(jì)過(guò)程中,經(jīng)常需要一定的創(chuàng)造力(不妨稱之為數(shù)字管道膠帶)才能夠保證設(shè)計(jì)的順利完成。過(guò)去8年時(shí)間里,我曾經(jīng)目睹許多優(yōu)秀工程師利用這一方法出色地完成了許多工作,而他們采用的最主要工具就是FPGA Editor。

- 關(guān)鍵字: 賽靈思 FPGA Editor

cpld/fpga介紹

您好,目前還沒(méi)有人創(chuàng)建詞條cpld/fpga!

歡迎您創(chuàng)建該詞條,闡述對(duì)cpld/fpga的理解,并與今后在此搜索cpld/fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)cpld/fpga的理解,并與今后在此搜索cpld/fpga的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司