- 電腦繡花機是隨著計算機技術、電子技術、機械加工技術的應用發展而不斷發展起來的光、機、電一體化設備。嵌入式系統的發展及研究風頭正勁,其在數字機床、智能控制等方面的應用正逐漸改變著傳統的工業生產和服務方

- 關鍵字:

FPGA ARM 電腦繡花機 控制系統

- 1、前言 隨著計算機技術的高速發展,各工業發達國家投入巨資,對現代制造技術進行研究開發,提出了全新的制造模式,其核心思想之一是柔性化制造,制造系統能夠隨著加工條件的變化動態調整。目前,各類MCU 快速

- 關鍵字:

CPLD DSP 可重構 仿真

- 隨著工藝節點和裸片尺寸不斷縮小,采用倒裝芯片封裝IC器件的消費電子產品的數量日益增加。但是,倒裝芯片封...

- 關鍵字:

SoC 設計 封裝協同 芯片 FPGA

- 介紹了一種利用ALTERA公司的復雜可編程邏輯器件(CPLD)快速卷積法實現數字濾波器的設計。

- 關鍵字:

CPLD FIR 數字濾波器

- 介紹了一款PC104總線多功能擴展卡設計。采用了復雜可編程邏輯器件(CPLD)技術,集成了多路模擬量輸入/輸出、帶光電隔離的開關量輸入/輸出及一個正交解碼電路,接口協議與臺灣研華PC工控機ISA總線板卡兼容,滿足了嵌入式控制系統高集成度的設計要求,在實際應用中獲得了良好的效果。

- 關鍵字:

CPLD 104 PC 總線

- 高性能系統設計師在滿足關鍵時序余量的同時要力爭獲得更高性能,而存儲器>存儲器接口設計則是一項艱巨挑戰。雙倍數據速率SDRAM和4倍數據速率SDRAM都采用源同步接口來把數據和時鐘(或選通脈沖)由發射器

- 關鍵字:

FPGA 助力 存儲器 接口設計

- 摘要:現代通信系統中,數字化已成為發展的必然趨勢,數字信號處理則是數字系統中的重要環節。在數字信號處理方面提出一種級聯信號處理器的FPGA實現方案,用以取代昂貴的專用數字處理芯片。首先對級聯信號處理器做了

- 關鍵字:

FPGA 級聯 信號處理器

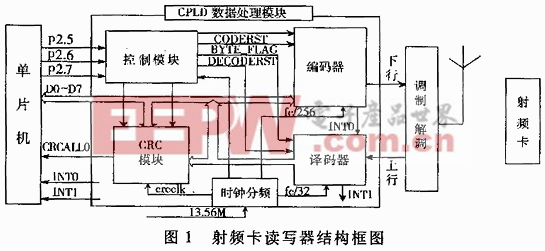

- 提出了一種射頻卡讀寫器數字處理模塊的設計方案,特點是利用單片CPLD器件實現了讀寫器編碼、譯碼和差錯處理功能,系統體積小,性能穩定。該方案采用了原理圖和VHDL相結合的靈活設計,給出了一種快速CRC-CCITT并行實現的方法。

- 關鍵字:

應用 讀寫器 射頻卡 CPLD 射頻

- 先進的視頻編碼(AVC)正在慢慢地超越數字視頻的主要標準。也稱之為H.264和MPEG-4part10,其AVC編碼在1Mbit/s~2...

- 關鍵字:

視頻編碼器 AVC編碼 FPGA

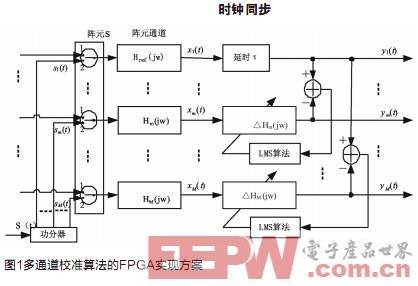

- 數字信號處理模塊是接收機系統的核心部分,系統要求數字信號處理模塊能實時處理ADC變換后的數字信號,并用軟件的方法來實現大量的無線電功能,這些功能包括:多通道校準、編解碼、調制解調、濾波、同步、盲均衡、

- 關鍵字:

FPGA 多通道 校準 算法

- 摘要:提出一種基于DSP和FPGA技術的低信噪比情況下雷達信號檢測技術的工作原理與硬件實現方法,采用數字化的處理方法處理信息,取代傳統使用的模擬檢測技術,并對實現的檢測方法和關鍵算法做了詳細介紹。

關鍵詞:高

- 關鍵字:

FPGA DSP 低信噪比 雷達信號

- 對于FFT而言,很多領域都提出了其高速實時運算的要求。利用FFT IP核實現FFT算法,并在cycloneⅡ系列的EP2C70F896C8器件上設計出處理速度為69.58 MHz的24位512點復數FFT處理器需29.3 μs,該方法具有效率高、速度快、周期短、靈活性強等特點。仿真結果表明此方法具有良好性能。

- 關鍵字:

FPGA FFT IP核

- 本文主要研究了多通道校準算法在FPGA上的同步實現問題。介紹FPGA時鐘同步設計的基本原理以及用Xilinx公司的FPGA芯片Xc2v8000ff1152-5實現了多通道校準的同步算法,極大提高了系統穩定性。

- 關鍵字:

ADC FPGA 多通道校準 同步實現 200907

- 通用異步收發器(Universal Asynchronous Receiver Transmitter,UART)是數字通信領域流行和廣泛使用的一種接口設備,主要用來控制符合RS 232-C協議的計算機與串行設備間的通信。普通串行外設和計算機間的通信,一般使

- 關鍵字:

FPGA UART 設計實現

cpld/fpga介紹

您好,目前還沒有人創建詞條cpld/fpga!

歡迎您創建該詞條,闡述對cpld/fpga的理解,并與今后在此搜索cpld/fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473