- 介紹了一種基于復雜可編程邏輯器件(CPLD)的壓電生物傳感器檢測電路。該檢測電路以高性能CPLD(MAX7128)...

- 關鍵字:

FPGA CPLD 生物傳感器 檢測電路

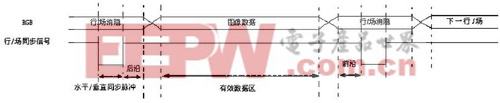

- 基于FPGA及DSP Builder的VGA接口設計,本文基于DSP Builder的VGA接口設計方法,對VGA接口時序和系統設計需求進行了介紹,并在硬件平臺下實現一維與二維信號的顯示。

VGA接口標準

VGA顯像原理

顯示器通過光柵掃描的方式,電子束在顯示屏幕上

- 關鍵字:

接口 設計 VGA Builder FPGA DSP 基于

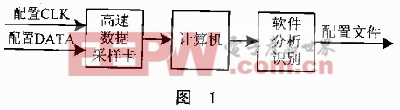

- 在現代電子系統設計中,由于可編程邏輯器件的卓越性能、靈活方便的可升級特性,而得到了廣泛的應用。由于大規模高密度可編程邏輯器件多采用SRAM工藝,要求每次上電,對FPGA器件進行重配置,這就使得可以通過監視配置

- 關鍵字:

保密性 問題 FPGA 工藝 SRAM 基于

- ASIC、FPGA和DSP的應用領域呈現相互覆蓋的趨勢,使設計人員必須在軟件無線電結構設計中重新考慮器件選擇...

- 關鍵字:

FPGA ASIC DSP 軟件無線電

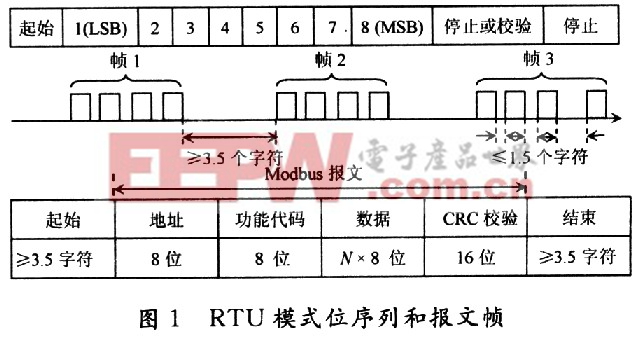

- Modbus協議是一個應用廣泛的工業現場總線協議,鑒于其簡單、開放、幀格式緊湊等優點,于2008年正式成為我國國家標準。介紹一種通過Cyclone系列FPGA實現Modbus RTU模式的方法,首先給出一個可以通用于Modbus主設備和從設備的協議接口單元,然后基于該接口設計了一個通用的Modbus從設備協處理器。實踐證明該方法能夠滿足工業環境的通訊要求,此外,該方法在其他FPGA上也具有一定通用性和推廣價值。

- 關鍵字:

實現 FPGA 協議 通信 Modbus 功率模塊

- Altera公司今天發布Stratix® V系列FPGA,適用于支持Micron技術公司的下一代低延時DRAM (RLDRAM® 3存儲器)。Stratix V FPGA采用新的存儲器體系結構,降低延時,高效實現FPGA業界最好的系統性能。Stratix V FPGA為網絡設備生產商提供存儲器接口解決方案,支持在互聯網上迅速有效的傳送視頻、語音和數據。

Micron公司業務開發高級經理Bruce Franklin表示:“Micron的下一代RLDRAM 3存儲器專門設

- 關鍵字:

Altera FPGA Stratix

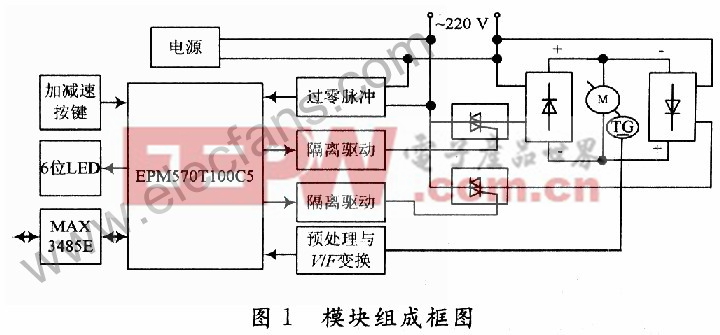

- 基于 CPLD EPM570T100C5的通用直流調速模塊設計,本文針對常見調速應用,采用可控硅做為調速元件,采用EPM570T100C5設計和實現了一個通用直流調速模塊,為實現遠距離控制內置了RS 485通信和簡單通信協議。采用EPM570T100C5作為控制核心,電路簡潔,輸出控制脈沖精確

- 關鍵字:

調速 模塊 設計 直流 通用 CPLD EPM570T100C5 基于

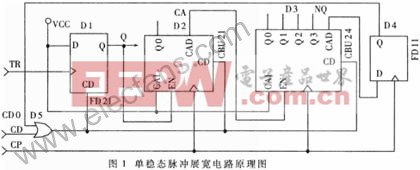

- 基于CPLD器件設計的單穩態電路,隨著電子技術特別是數字集成電路技術的迅猛發展,市面上出現了FPGA、CPLD等大規模數字集成電路,并且其工作速度和產品質量不斷提高。利用大規模數字集成電路實現常規的單穩態集成電路所實現的功能,容易滿足寬度、精

- 關鍵字:

穩態 電路 設計 器件 CPLD 基于

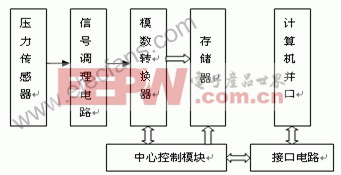

- 基于CPLD的水下沖擊波記錄儀的設計,1.引言

隨著大規模集成電路和單片機的迅速發展,復雜可編程邏輯器件(CPLD)具有使用靈活、可靠性高、功能強大的優點,在電子產品設計中得到了廣泛的應用。CPLD可實現在系統編程,重復多次,而且還兼容IEEE1

- 關鍵字:

記錄儀 設計 沖擊波 水下 CPLD 基于

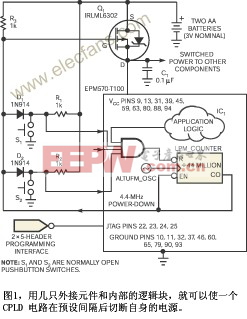

- 節省電池能量的系統斷電電路CPLD,今天,大多數的CPLD(復雜可編程邏輯器件)都采用可減少功耗的工作模式,但當系統未使用時,應完全切斷電源以保存電池能量,從而實現很多設計者的終極節能目標。圖1描述了如何在一片CPLD 上增加幾只分立元件,實現一

- 關鍵字:

電路 CPLD 斷電 系統 電池 能量 節省

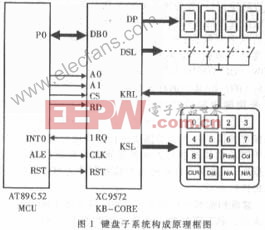

- 基于CPLD的專用鍵盤接口芯片的方案設計,在單片機應用系統中,存在多種形式的外部數據輸入接口界面,例如RS-232C串行通信、鍵盤輸入等[1,4] 。其中利用鍵盤接口輸入數據,是實現現場實時調試、數據調整和控制最常用的方法。單片機的外圍鍵盤擴展電路有多種實

- 關鍵字:

芯片 方案設計 接口 鍵盤 CPLD 專用 基于

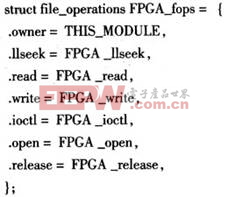

- ARM920T基于Linux平臺下的FPGA驅動開發,Linux操作系統的全稱是GNU/Linux,它是由GNU工程和Linux內核兩個部分共同組成的一個操作系統。該系統中所有組件的源代碼都是自由的,可以有效保護學習成果,因而在嵌入式領域得到了廣泛的應用。

FPGA是英文Field

- 關鍵字:

驅動 開發 FPGA 平臺 基于 Linux ARM920T

- 摘要:從實際工程應用出發,研究了在基于FPGA上快速傅里葉變換實現線性卷積的方法,并搭建了一個基于Altera的EP2S60硬件處理平臺,利用Altera提供的FFT IP核,在100 MHz系統時鐘下,數據吞吐率可達100 Ms/s,

關鍵

- 關鍵字:

FPGA 線性卷積

cpld/fpga介紹

您好,目前還沒有人創建詞條cpld/fpga!

歡迎您創建該詞條,闡述對cpld/fpga的理解,并與今后在此搜索cpld/fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473