- 波長信號的解調是實現光纖光柵傳感網絡的關鍵,基于現有的光纖光柵傳感器解調方法,提出一種基于FPGA的雙匹配光纖光柵解調方法,此系統是一種高速率、高精度、低成本的解調系統,并且通過引入雙匹配光柵有效地克服了雙值問題同時擴大了檢測范圍。分析了光纖光柵的測溫原理并給出了該方案軟硬件設計,綜合考慮系統的解調精度和FPGA的處理速度給出了基于拉格朗日的曲線擬合算法。

- 關鍵字:

FPGA 光纖光柵 解調系統

- 本次設計應用V /F轉換器實現高分辨率AD轉換,具有較高的滿刻度頻率響應、低功耗和較低的非線性度等特點,廣泛應用于儀器儀表對溫度的控制中,滿足對設定溫度控制穩定性的要求。在系統設計中采用CPLD實現頻率計數功能,是數字系統精確測量頻率一種方法:在采樣時間內同時對標準頻率信號和被測頻率信號計數。采樣完成后,把二者的計數值相比,再乘以標準頻率就可以得到被測頻率的精確值。

- 關鍵字:

CPLD AD轉換 高分辨率 電路設計

- 為滿足用戶的多種設計需求,Altera公司 今天發布其28-nm器件系列產品,為業界提供最全面的器件選擇。Altera在Cyclone V和Arria V FPGA新系列、最新擴展的Stratix V FPGA以及此前發布的HardCopy V ASIC系列中為用戶提供突出不同產品優勢的解決方案。

- 關鍵字:

Altera Stratix V FPGA

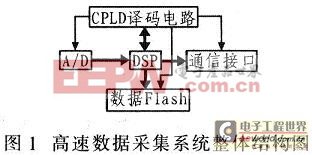

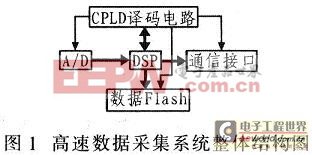

- 基于DSP和MAX1420的高速數據采集系統設計,1 引言 數據采集系統是通信與信息技術領域中重要的功能模塊,應用廣泛。而傳統的數據采集系統大多以單片機或中規模數字電路為核心,其模數轉換器(A/D轉換器)采樣速率較低。顯然傳統數據采集系統不能完全滿足高速

- 關鍵字:

DSP 數據 采集 CPLD USB

- 摘要:探測系統對輸入的空間瞬態光輻射信號進行實時識別處理,反演估算出空間瞬態信號能量大小并報告發生時刻。采用dsp+cpld的數字處理方案,利用dsp的高速數字信號處理特性及cold的復雜邏輯可編程特性,可實現對

- 關鍵字:

CPLD DSP 空間瞬態 光輻射

- 摘要:經典的碼盤數字測速方法有M法、T法、M/T法,但都有一定的不足。為了克服原有方法的不足,設計并實現了一種在較大速度范圍都有良好精度和良好快速性的測速方法。電路采用FPGA實現,測速得到的數據通過PCI總線從

- 關鍵字:

FPGA PCI 高精度 測速

- 采用FPGA的模擬動態濾波器,在結構上簡易,性能上穩定,測試和設計都十分的方便。FPGA的使用,能根據具體要求很方便的改變控制信號,同時實現超聲診斷儀中多個模塊并行工作,也為以后的更多模擬部分數字化提供了基礎。

- 關鍵字:

FPGA 超聲診斷儀 動態 濾波器

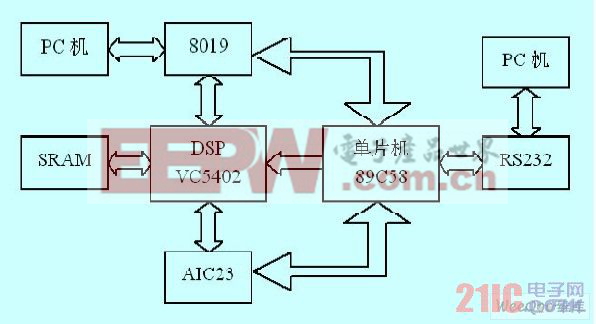

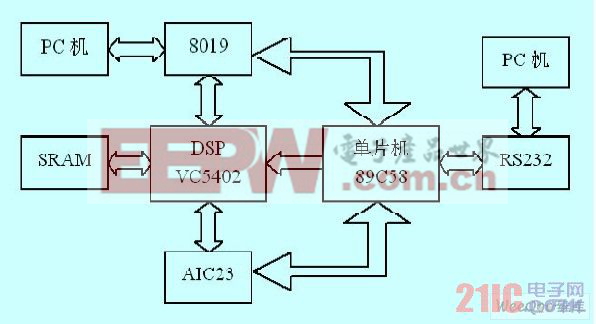

- 基于DSP 的高速信號采集系統設計, 1 引言

數據采集技術是一項基本的實用性技術,已被廣泛地應用于測量、檢測、控制、診斷等各個領域。隨著電子技術, 計算機技術和通信技術的迅猛發展, 國內外用數字信號處理的辦法檢測, 采集, 分析, 處理各種數據

- 關鍵字:

DSP 信號 采集 CPLD

- 本文分析了IL-E2型TDI-CCD 芯片的工作過程和對驅動信號的要求,在此基礎上設計出合理的時序電路, 為了滿足在實際工作中像移速度異速匹配的要求,在時序電路的設計中時序發生部分是可調的。這種設計方案簡單、可靠、實用。

- 關鍵字:

FPGA CCD 相機 時序

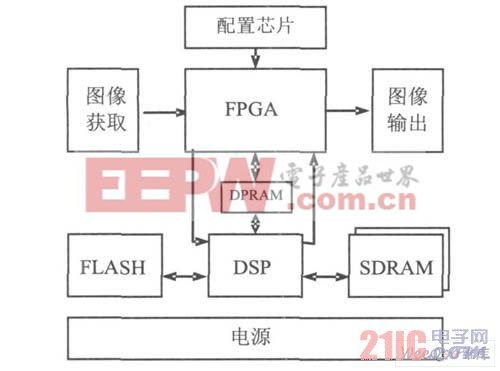

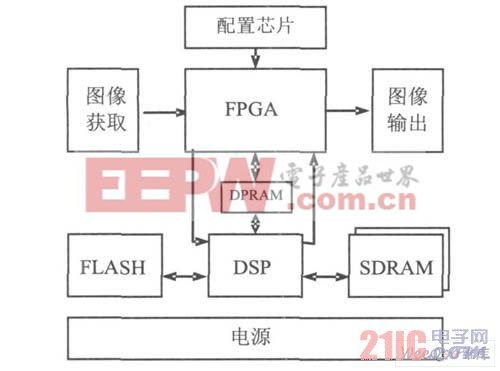

- 基于FPGA+ DSP的實時圖像處理系統設計與實現,摘 要: 針對圖像處理系統計算量大、實時性高和體積小的要求, 研制了一種以DSP為主處理器FPGA 為輔處理器的高性能實時圖像處理系統。利用這兩種芯片的各自特點, 將算法分成兩部分分別交由FPGA 和DSP處理, 大大提高

- 關鍵字:

FPGA,DSP

- 1 引 言

微型計算機原理幾乎是所有理工科類大學生的必修課目之一, 其重要性不言而喻。然而大多數教學側重于應用方面, 對計算機的結構及工作原理涉之不深, 因為無法做一個CPU 來演示。這樣學生不能真正了解

- 關鍵字:

8085A FPGA CPU 結構分析

- 隨著FPGA融入越來越多的能力,對有效調試工具的需求將變得至關重要。對內部可視能力的事前周密計劃將能使研制組采用正確的調試戰略,以更快完成他們的設計任務。

“我知道我的設計中存在一個問題,但我沒有很

- 關鍵字:

FPGA 邏輯分析 電路 調試技術

- 全球電子設計創新領先企業Cadence設計系統公司,今天宣布在幫助ASIC與FPGA設計者們提高驗證效率方面取得最新重大進展。加上對最新Accellera Universal Verification Methodology (UVM) 1.0業界標準的全面支持,600多種新功能擴展了指標驅動型驗證(MDV)的范圍,幫助工程師實現更快、更全面的驗證閉合與硅實現。

- 關鍵字:

Cadence FPGA

- 摘要:基于高階累積量的數字調制信號識別算法在低信噪比環境下識別率較低。針對這一問題,提出了高階累積量的改進算法,通過調整特征參數的判別順序先識別出MASK信號的方式,取得了較好的效果。討論了該算法的FPGA設

- 關鍵字:

FPGA 高階累積量 調制識別 改進算法

- 自 1985 年 Xilinx 向市場推出全球首款現場可編程門陣列 (FPGA) 以來,成千上萬的設計工程師充分利用其卓越的靈活性、可重復編程性、功能性和出眾的高性能及高容量構建了各種令人稱贊的創新型產品,使我們的日常生活

- 關鍵字:

FPGA 案例

cpld/fpga介紹

您好,目前還沒有人創建詞條cpld/fpga!

歡迎您創建該詞條,闡述對cpld/fpga的理解,并與今后在此搜索cpld/fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473