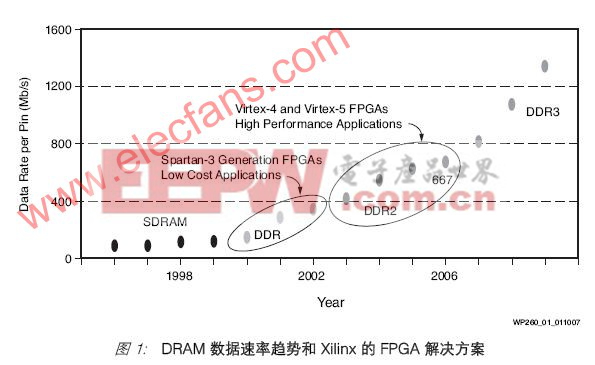

- 采用Xilinx 和FPGA的DDR2 SDRAM存儲器接口控制器的設計,本白皮書討論各種存儲器接口控制器設計所面臨的挑戰和 Xilinx 的解決方案,同時也說明如何使用 Xilinx軟件工具和經過硬件驗證的參考設計來為您自己的應用(從低成本的 DDR SDRAM 應用到像 667 Mb/sDDR2 SDRAM 這樣的更

- 關鍵字:

接口 控制器 設計 存儲器 SDRAM Xilinx FPGA DDR2 采用

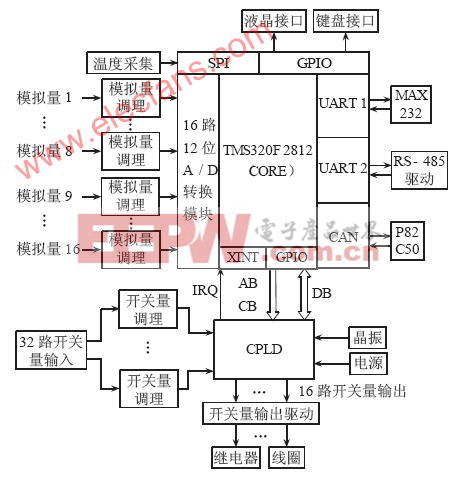

- 采用CPLD與μC/OS -Ⅱ的斷路器智能控制單元設計,本文介紹的智能控制單元采用數字信號處理器(DSP)及嵌入式實時操作系統完成各種數據的處理、通信和算法的設計,而狀態量的采集和執行信號輸出將由復雜可編程邏輯器(CPLD)完成,主要是基于CPLD內部硬件電路結構的可靠性

- 關鍵字:

單元 設計 智能控制 斷路器 CPLD C/OS 采用

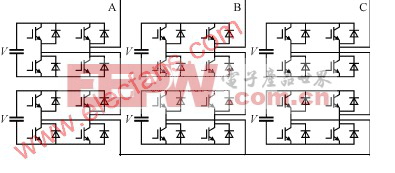

- 采用DSP與CPLD的三相五電平變頻器PWM脈沖發生器,1 引言 近年來,多電平變換器成為電力電子研究的熱點之一,它主要面向中壓大功率的應用場合。目前,有三種基本的多電平變換器拓撲結構[1]:①二極管箝位型;②飛跨電容型;③級聯型。 幾種拓撲結構各有其優缺點,但相

- 關鍵字:

PWM 脈沖 發生器 變頻器 電平 DSP CPLD 三相五 采用

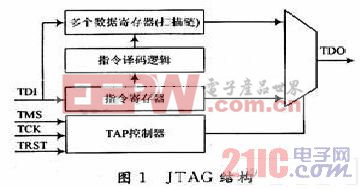

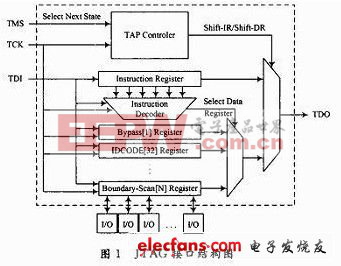

- 系統結構框圖如圖1。其硬件結構比較簡單,主要由單片機P89C51RD、RS-232/TTL接口電路MAX232和可編程邏輯器件FPGA三部分組成。單片機P89C51RD2是上位PC機和FPGA的連接紐帶,它通過并口發送數據給FPGA,另一邊通過RS-2

- 關鍵字:

FPGA 單片機 可調延時模塊

- 例1:FPGA驅動LED靜態顯示 --文件名:decoder.vhd --功能:譯碼輸出模塊,LED為共陽接法 --最后修改日期:2004.3.24 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL;

- 關鍵字:

FPGA VHDL LED 驅動

- 1 引 言 UART 即通用異步收發器,他廣泛使用串行數據傳輸協議。UART 功能包括微處理器接口、用于數據傳輸的緩沖器(Buffer)、幀產生、奇偶校驗、并串轉換,用于數據接收的緩沖器、幀產生、奇偶校驗、串并轉換等。

- 關鍵字:

FPGA UART 電路實現

- “我們在NI CompactRIO平臺上開發的SVC全數字控制系統,大大縮短了產品上市的時間又保證了系統的穩定性。”挑戰:電弧爐、軋鋼機等大型工業設備在為企業創造產值的同時也帶來了無功分量和高次諧波等危害,

- 關鍵字:

FPGA 無功補償 控制器

- 電子產品世界,為電子工程師提供全面的電子產品信息和行業解決方案,是電子工程師的技術中心和交流中心,是電子產品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網絡家園

- 關鍵字:

DSP FPGA 汽車電子

- 電子產品世界,為電子工程師提供全面的電子產品信息和行業解決方案,是電子工程師的技術中心和交流中心,是電子產品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網絡家園

- 關鍵字:

激光 DSP FPGA 控制單元

- 引言可編程衰減器位于基站和終端之間,通過對射頻信號的衰減控制,實現對無線信號的模擬,從而實現對測試場景的模擬。可編程衰減器提供多個數控接口,從小到大可以構建各個層次的測試網絡。所構成的衰減矩陣通過模擬

- 關鍵字:

FPGA 可編程 衰減器

- 基于ARM+FPGA的重構控制器設計, 可重構技術是指利用可重用的軟硬件資源,根據不同的應用需求,靈活地改變自身體系結構的設計方法。常規SRAM工藝的FPGA都可以實現重構,利用硬件復用原理,本文設計的可重構控制器采用ARM核微控制器作為主控制器

- 關鍵字:

控制器 重構 設計 需求 不同 作為 FPGA 可以 靈活 系統

- Linux下CPLD驅動程序,========================================================================== */

/* */

/* Filename.c

- 關鍵字:

驅動程序 CPLD Linux

- 安富利公司 (NYSE: AVT) 旗下安富利電子元件亞洲 (Avnet Electronics Marketing Asia)與賽靈思公司 (NASDAQ: XLX) 日前宣布啟動亞洲區X-fest 研討會注冊。X-fest 是深受 FPGA、DSP 和嵌入式系統開發人員歡迎的、為期一天的培訓活動。

- 關鍵字:

賽靈思 FPGA X-fest

- 基于DSP的CPLD軟件更新方案研究, 0引言 在現代導航計算機系統朝著微型化發展的過程中,采用高性能數字信號處理器和可編程邏輯器件方案實現的導航計算機系統有著很高的性能優勢。在本課題組研制的基于浮點型DSP和復雜可編程邏輯器件(CPLD)結構的嵌

- 關鍵字:

方案 研究 更新 軟件 DSP CPLD 基于

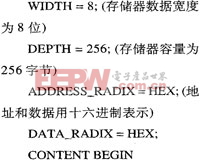

- 基于FPGA技術的存儲器設計及其應用,復雜可編程邏輯器件—FPGA技術在近幾年的電子設計中應用越來越廣泛。FPGA具有的硬件邏輯可編程性、大容量、高速、內嵌存儲陣列等特點使其特別適合于高速數據采集、復雜控制邏輯、精確時序邏輯等場合的應用。而應

- 關鍵字:

及其 應用 設計 存儲器 FPGA 技術 基于

cpld/fpga介紹

您好,目前還沒有人創建詞條cpld/fpga!

歡迎您創建該詞條,闡述對cpld/fpga的理解,并與今后在此搜索cpld/fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473