cpld/fpga 文章 最新資訊

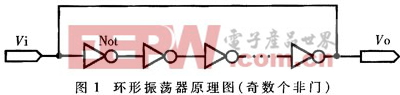

采用CPLD的片內(nèi)環(huán)形振蕩器的方案設(shè)計(jì)

- 采用CPLD的片內(nèi)環(huán)形振蕩器的方案設(shè)計(jì),本文介紹一種通用的基于CPLD的片內(nèi)振蕩器設(shè)計(jì)方法,它基于環(huán)形振蕩器原理,只占用片上普通邏輯資源(LE),無需使用專用邏輯資源(如MaxII中的UFM),從而提高了芯片的資源利用率;振蕩頻率可在一定范圍內(nèi)調(diào)整,振蕩輸出

- 關(guān)鍵字: 方案設(shè)計(jì) 振蕩器 內(nèi)環(huán) CPLD 采用

FPGA/CPLD設(shè)計(jì)思想與技巧簡介

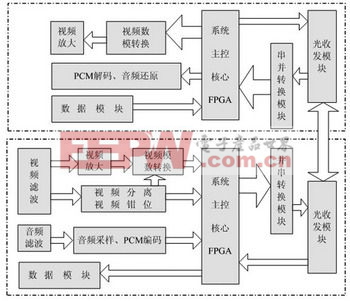

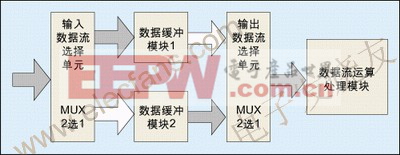

- FPGA/CPLD設(shè)計(jì)思想與技巧簡介,本文討論的四種常用FPGA/CPLD設(shè)計(jì)思想與技巧:乒乓操作、串并轉(zhuǎn)換、流水線操作、數(shù)據(jù)接口同步化,都是FPGA/CPLD邏輯設(shè)計(jì)的內(nèi)在規(guī)律的體現(xiàn),合理地采用這些設(shè)計(jì)思想能在FPGA/CPLD設(shè)計(jì)工作中取得事半功倍的效果。 F

- 關(guān)鍵字: 簡介 技巧 設(shè)計(jì)思想 FPGA/CPLD

一種基于CPLD的16位VFC式AD轉(zhuǎn)換器設(shè)計(jì)

- 隨著科技的飛速發(fā)展、高分辨率的數(shù)模混合電路的應(yīng)用不斷深入,電路設(shè)計(jì)日趨復(fù)雜,精度越來越高,所以高精度AD轉(zhuǎn)換電路的設(shè)計(jì)就成了儀器儀表及各種測(cè)量控制系統(tǒng)的難點(diǎn)。本系統(tǒng)來源于儀器儀表的溫控系統(tǒng)設(shè)計(jì),采用高精

- 關(guān)鍵字: CPLD VFC AD轉(zhuǎn)換器

基于FPGA的高精度時(shí)間數(shù)字轉(zhuǎn)換電路設(shè)計(jì)

- 摘要:本文介紹一種基于 FPGA高精度時(shí)間數(shù)字轉(zhuǎn)換電路的設(shè)計(jì)方法,利用片內(nèi)鎖相環(huán)(PLL)和環(huán)形移位寄存器,采用不高的系統(tǒng)時(shí)鐘便可得到很高的時(shí)間分辨率,且占用較少邏輯資源。可作為功能電路獨(dú)立使用,也可作為 IP核

- 關(guān)鍵字: FPGA 高精度 電路設(shè)計(jì) 數(shù)字轉(zhuǎn)換

cpld/fpga介紹

您好,目前還沒有人創(chuàng)建詞條cpld/fpga!

歡迎您創(chuàng)建該詞條,闡述對(duì)cpld/fpga的理解,并與今后在此搜索cpld/fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)cpld/fpga的理解,并與今后在此搜索cpld/fpga的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司