asic-to-fpga 文章 最新資訊

Xilinx UltraScale?:為您未來架構(gòu)而打造的新一代架構(gòu)

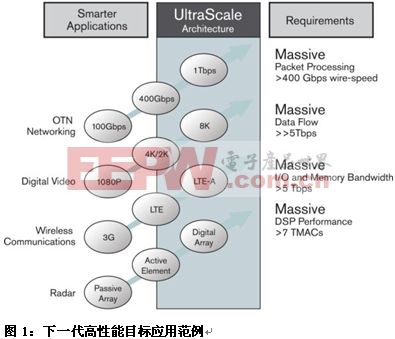

- Xilinx UltraScale? 架構(gòu)針對要求最嚴苛的應(yīng)用,提供了前所未有的ASIC級的系統(tǒng)級集成和容量。

- 關(guān)鍵字: Xilinx UltraScale ASIC 存儲器

Digilent Nexys3 FPGA開發(fā)板評測(三)

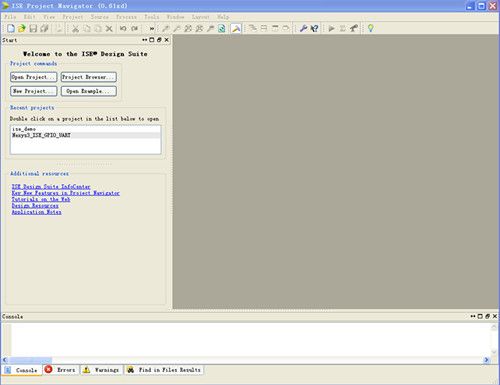

- 演示程序 設(shè)計工具對于選擇FPGA進行設(shè)計是非常重要的一個部分,Xilinx公司提供了強大的集成設(shè)計工具ISE Design Suite。Spartan-6系列FPGA芯片也是適用于Xilinx所倡導(dǎo)的目標設(shè)計平臺,豐富的IP資源是設(shè)計變得更加靈活、方便。Digilent也提供了豐富的Demo程序和參考設(shè)計,可以在其官網(wǎng)免費下載。 本文的演示程序分為兩種版本,分別基于ISE和EDK。可以了解如何在ISE環(huán)境下進行FPGA的設(shè)計以及如何用EDK搭建系統(tǒng)平臺。該演示程序主要是如何控制N

- 關(guān)鍵字: Digilent FPGA

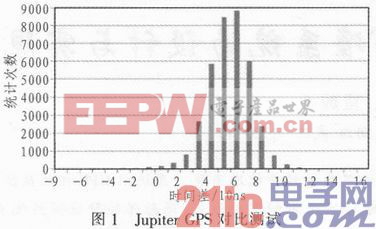

基于GPS的恒溫晶振頻率校準系統(tǒng)的設(shè)計與實現(xiàn)

- 針對目前廣泛對高精度頻率源的需求,利用FPGA設(shè)計一種恒溫晶振頻率校準系統(tǒng)。系統(tǒng)以GPS接收機提供的秒脈沖信號為基準源,通過結(jié)合高精度恒溫晶振短期穩(wěn)定度高與GPS長期穩(wěn)定特性好、跟蹤保持特性強的優(yōu)點,設(shè)計數(shù)字鎖相環(huán)調(diào)控恒溫晶振的頻率。詳細闡述系統(tǒng)的設(shè)計原理及方法,測試結(jié)果表明,恒溫晶振的頻率可快速被校準到10 MHz,頻率偏差小于0.01Hz,具有良好的長期穩(wěn)定性,適合在多領(lǐng)域中作為時間頻率的標準。

- 關(guān)鍵字: 頻率校準 恒溫晶振 數(shù)字鎖相環(huán) FPGA

Xilinx首個ASIC級UltraScale可編程架構(gòu)-常見問題

- 賽靈思將在2013年7月10日宣布推出什么產(chǎn)品?

- 關(guān)鍵字: 賽靈思 UltraScale ASIC

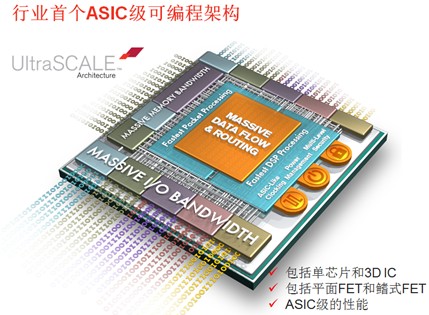

Xilinx首個ASIC級可編程架構(gòu)20nm All Programmable器件開始投片

- All Programmable FPGA、SoC和3D IC的全球領(lǐng)先企業(yè)賽靈思公司 (Xilinx, Inc. (NASDAQ:XLNX) )日前宣布,延續(xù)28nm工藝一系列行業(yè)創(chuàng)新,在20nm工藝節(jié)點再次推出兩大行業(yè)第一:投片半導(dǎo)體行業(yè)首款20nm器件,也是可編程邏輯器件(PLD)行業(yè)首款20nm All Programmable器件;發(fā)布行業(yè)第一個ASIC級可編程架構(gòu)UltraScale?。

- 關(guān)鍵字: 賽靈思 ASIC UltraScale

三原則助力FPGA系統(tǒng)設(shè)計

- 一.面積與速度的平衡互換原則 這里的面積指的是FPGA的芯片資源,包括邏輯資源和I/O資源等;這里的速度指的是FPGA工作的最高頻率(和DSP或者ARM不同,F(xiàn)PGA設(shè)計的工作頻率是不固定的,而是和設(shè)計本身的延遲緊密相連)。 在實際設(shè)計中,使用最小的面積設(shè)計出最高的速度是每一個開發(fā)者追求的目標,但是“魚和熊掌不可兼得”,取舍之間展示了一個開發(fā)者的智慧。 1.速度換面積 速度優(yōu)勢可以換取面積的節(jié)約。面積越小,就意味著可以用更低的成本來實現(xiàn)產(chǎn)品的功能。速度換面積的

- 關(guān)鍵字: FPGA DSP

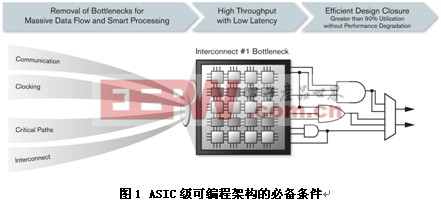

Xilinx UltraScale 架構(gòu)—業(yè)界首款A(yù)SIC級All Programmable架構(gòu)

- 現(xiàn)在,人們需要采用一種創(chuàng)新型架構(gòu)來管理數(shù)百Gbps的系統(tǒng)性能,以實現(xiàn)全線速下的智能處理能力,并擴展至Tb級性能和每秒10億次浮點運算水平。

- 關(guān)鍵字: 賽靈思 DSP ASIC UltraScale RAM

常見問題解答:賽靈思采用首個ASIC級UltraScale可

- 1. 賽靈思將在2013年7月10日宣布推出什么產(chǎn)品? 賽靈思宣布20nm兩項新的行業(yè)第一,延續(xù)28nm工藝節(jié)點上一系列業(yè)界創(chuàng)新優(yōu)勢: middot; 賽靈思宣布開始投片半導(dǎo)體行業(yè)首款20nm器件以及投片PLD行業(yè)首款20nm All

- 關(guān)鍵字: UltraScale ASIC 賽靈思 可編程

物聯(lián)網(wǎng)融合自動化推動高效生產(chǎn)模式變革

- 伴隨物聯(lián)網(wǎng)技術(shù)應(yīng)用的擴展,工業(yè)生產(chǎn)與其結(jié)合的趨勢越發(fā)明顯,如今自動化生產(chǎn)模式與物聯(lián)網(wǎng)技術(shù)更有不斷融合的趨勢,或帶來更高效的生產(chǎn)模式變革。 現(xiàn)代工業(yè)生產(chǎn)尤其是自動化生產(chǎn)過程中,要用各種傳感器來監(jiān)視和控制生產(chǎn)過程中的各個參數(shù),使設(shè)備工作在正常狀態(tài)或最佳狀態(tài),并使產(chǎn)品達到最好的質(zhì)量。因此可以說,沒有眾多的優(yōu)良的傳感器,現(xiàn)代化生產(chǎn)也就失去了基礎(chǔ)。 專家表示自物聯(lián)網(wǎng)誕生以來,很多工業(yè)自動化業(yè)內(nèi)人士認為物聯(lián)網(wǎng)將為工業(yè)自動化加速發(fā)展增加新的引擎,隨著物聯(lián)網(wǎng)與工業(yè)自動化的深度融合。 目前物聯(lián)網(wǎng)與工業(yè)

- 關(guān)鍵字: 物聯(lián)網(wǎng) FPGA SoC

asic-to-fpga介紹

您好,目前還沒有人創(chuàng)建詞條asic-to-fpga!

歡迎您創(chuàng)建該詞條,闡述對asic-to-fpga的理解,并與今后在此搜索asic-to-fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對asic-to-fpga的理解,并與今后在此搜索asic-to-fpga的朋友們分享。 創(chuàng)建詞條

熱門主題

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司