- 一種基于FPGA的接口電路設計, 摘 要:在航空電子系統中,經常需要對1553B總線和ARINC429總線進行雙向數據轉換以適應不同電子設備的接口要求。由于兩種總線標準傳輸協議不同,傳輸速率和數據格式有較大差異,常規系統需要多種專業數據轉換芯片以

- 關鍵字:

電路設計 接口 FPGA 基于

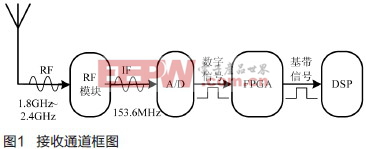

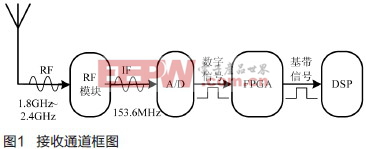

- 摘要:基于Xilinx FPGA設計出一種高性能數字接收機。該數字接收機由高速、高分辨率A/D和高性能FPGA構成。高速A/D實現中頻數字化,高性能FPGA實現數字下變頻、數字多相濾波、半帶抽取、匹配濾波和位同步功能,使得中頻載波為153.6MHz的TD-SCDMA信號,下變頻-抽取-濾波-位同步后得到高質量的采樣率為1.28MHz的基帶信號。

- 關鍵字:

FPGA 載波 A/D 201305

- 在FGPA戰場上,眾所皆知的頭號兩大對手就是Altera與Xilinx。一般認為這兩對手會在同一個戰場上爭個你死我活,然而經過多年的鏖戰,兩廠商已經從過去積極的正面廝殺對決,改而轉向較為保守的畫地為王,以既有優勢為基礎,固守疆域,進而轉化為更大的研發能量。

?

據了解,Xilinx在既有的28奈米FPGA市場已經打下穩定基礎,而目前xilinx也不側重在更先進製程上與對手爭個你死我活,反倒是穩扎穩打固守疆土,選擇將FPGA的可程式化優勢發揮到極致。Xilinx認為,可程式

- 關鍵字:

Altera FPGA

- 視頻顯示器市場分為:大批量應用,如臺式機、筆記本顯示器和電視機面板;中等批量應用,如小型人機接口(HMI)面板和大尺寸數字標牌。本文將探討的是大尺寸顯示器面板應用(表1),其中FPGA是一個備受關注的選擇,它可以滿

- 關鍵字:

FPGA 視頻顯示 接口

- 對于FPGA初學者而言,如何正確了解并理解FPGA的仿真是關鍵。應廣大FPGA初學者和愛好者要求,電子發燒友網編輯根 ...

- 關鍵字:

FPGA 核心知識 仿真

- 當今的設計工程師受到面積、功率和成本的約束,不能采用GHz級的計算機實現嵌入式設計。在嵌入式系統中,通常是由相對數量較少的算法決定最大的運算需求。使用設計自動化工具可以將這些算法快速轉換到硬件協處理器中。

- 關鍵字:

FPGA 協處理器 算法

- 1、電路設計與輸入 電路設計與輸入是指通過某些規范的描述方式,將工程師電路構思輸入給EDA工具。常用的 ...

- 關鍵字:

FPGA 設計流程 布線資源

- 在調試FPGA電路時要遵循必須的原則和技巧,才能降低調試時間,防止誤操作損壞電路。通常情況下,參考以下步驟執行 ...

- 關鍵字:

FPGA 硬件電路 調試必備

- 引 言門和人類文明是孿生的,它伴隨著人類文明的發展而躍動。21 世紀的今天,門更加突出了安全理念,強調了有效性:有效地防范、通行、疏散,同時還突出了建筑藝術的理念,強調門與建筑以及周圍環境整體的協調、和諧

- 關鍵字:

FPGA 自動門 控制設計

- ARM是目前全球最大的嵌入式芯片技術的IP提供商,其所擁有的IP已經成為眾多芯片設計公司采納的一種技術標準和開發平臺。所以基于ARM 內核的SoC已經成為嵌入式處理器的開發重點,可通過ARM實現LCD控制器來完成對嵌入式

- 關鍵字:

FPGA ARM 圖像

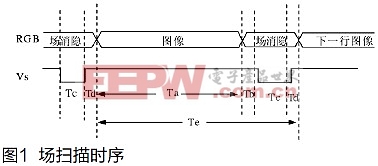

- 摘要:根據VGA(Video Graphic Array)的原理,采用VHDL硬件描述語言,設計了一種基于Zedboard FPGA板卡的圖像顯示方案。實驗結果表明,在FPGA實現圖片顯示,達到了預期的效果,依據該原理,可以實現圖像的采集及在VGA顯示屏上顯示的實現。

- 關鍵字:

VGA FPGA 圖片顯示 201304

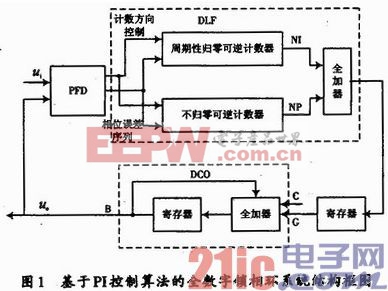

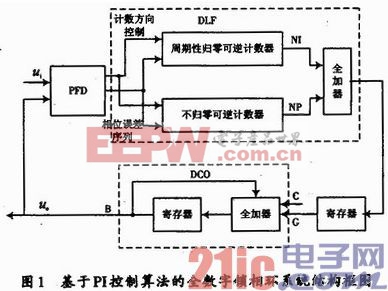

- 針對以往全數字鎖相環研究中所存在電路結構復雜、設計難度較大和系統性能欠佳等問題,提出了一種實現全數字鎖相環的新方法。該鎖相環以數字比例積分控制的設計結構取代了傳統的一些數字環路濾波控制方法。應用EDA技術完成系統設計,并進行計算機仿真。仿真結果表明:在一定的頻率范圍內,該鎖相環鎖定時間最長小于15個輸入信號周期,相位抖動小于輸出信號周期的5%,且具有電路結構簡單、環路性能好和易于集成的特點。

- 關鍵字:

比列積分控制 全數字鎖相環 超高速集成電路硬件描述語言 現場可編程門陣列

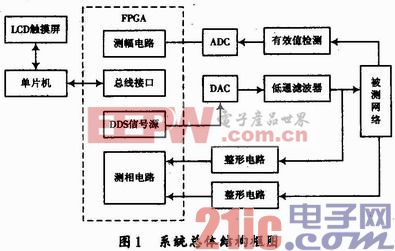

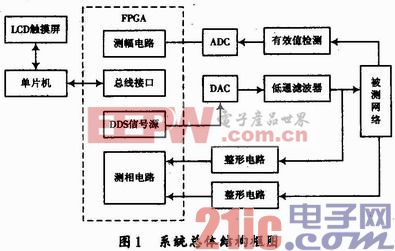

- 為設計一款便攜式頻率特性測試儀,該系統以大規模可縭程邏輯器件為實現載體,采用了基于FPGA體系結構的集成化設計方案,以VHDL為設計語言,設計了包含掃頻信號源、測幅、測相及顯示等電路,系統經峰值檢測和相位檢測分別完成了被測網絡的幅頻和相頻特性測量及曲線顯示,經調試功能上能滿足大部分系統要求,對RC串并聯電路進行測量誤差為0.4%;該系統具有探作簡單、成本低廉、性能穩定等特點,具有較強的實用價值與發展前景。

- 關鍵字:

頻率特性 現場可編程門陣列 直接數字頻率合成DDS 正弦信號

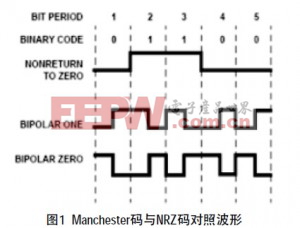

- 為了實現靶場時統終端輸出IRIG-B標準DC code信號,采用VHDL語言在FPGA邏輯電路中設計了DC code編碼器硬件電路,通過QuartusⅡ軟件建立工程文件對VHDL語言DC code編碼器電路進行編譯和仿真,獲得了符合IRIG-B標準的DC code信號。經過實踐驗證,該電路具有實現方法簡單、電路穩定性好、精度高的特點,實測同步精度小于1μs。

- 關鍵字:

IRIG-B FPGA code VHDL

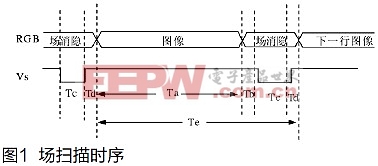

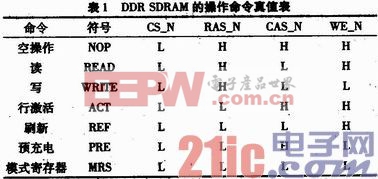

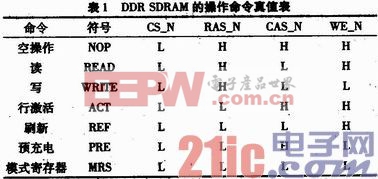

- 摘要 對DDR SDRAM的基本工作特性以及時序進行了分析與研究,基于FPGA提出了一種通用的DDRSDRAM控制器設計方案。在Modelaim上通過了軟件功能仿真,并在FPGA芯片上完成了硬件驗證。結果表明,該控制器能夠較好地完成DD

- 關鍵字:

控制器 設計 SDRAM DDR FPGA 基于

現場可編程門陣列(fpga)介紹

您好,目前還沒有人創建詞條現場可編程門陣列(fpga)!

歡迎您創建該詞條,闡述對現場可編程門陣列(fpga)的理解,并與今后在此搜索現場可編程門陣列(fpga)的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473