浮點:用 FPGA 嵌入式處理器實現(xiàn)您的構(gòu)想

賽靈思編譯器支持的 APU-FPU 單精度變量使用的資源較少。當 FPU 被占用時,雙精度操作將通過軟件仿真來執(zhí)行。

本文引用地址:http://www.cqxgywz.com/article/99212.htm軟 FPU 比軟件仿真法平均快 6 倍。單精度 FPU 通常比雙精度快 13%

將 APU-FPU 連接至 PowerPC 440

有兩種方法可將 APU-FPU 連接至 PowerPC 440 處理器:1、利用賽靈思 Platform Studio 設(shè)計工具中的 Base System Builder (BSB) 向?qū)?2、將 APU-FPU 單元添加至當前設(shè)計方案中即可。

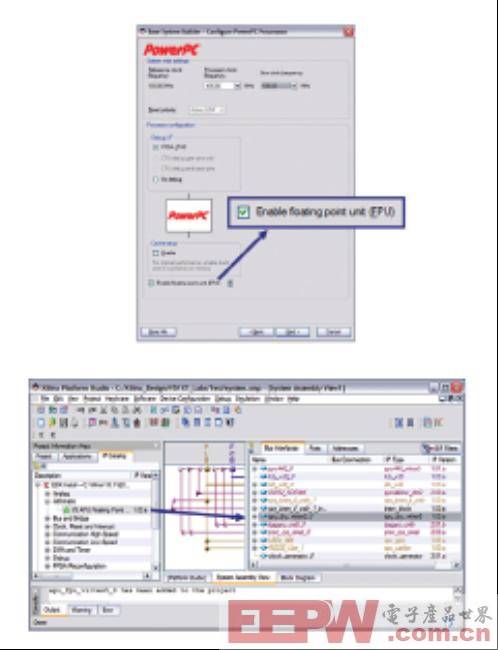

您首先需利用 BSB 向?qū)Т_定目標板和所期望的處理器(PowerPC 或 MicroBlaze™),然后通過一系列復(fù)選框和下拉菜單選擇設(shè)計中所需的 IP。借助 BSB 向?qū)В軌蜉p松快速地組裝并測試基礎(chǔ)處理器系統(tǒng)。您只需勾選您要選擇的 FPU 框,即可實現(xiàn)APU-FPU 連接(見圖 3 頂部)。該向?qū)Э蓪崿F(xiàn)一個經(jīng)過優(yōu)化能以處理器時鐘三分之一速率運行的雙精度 FPU。您也可定制更高時鐘速率的 FPU 和單精度 FPU。

如果不想使用向?qū)В部赏ㄟ^另一種方法來實現(xiàn),即按照系統(tǒng)組裝視圖拖動 IP Catalog 下的 APU- FPU IP,然后對 FPU 進行配置即可。圖 3 底部圖片顯示了 IP Catalog (見左下方)和系統(tǒng)組裝視圖中新添加的 FPU。右擊 FPU 并選擇 Configure IP,然后您便可選取想要的精度(單精度或雙精度)并確定您希望該 FPU 是針對低時延(三分之一時鐘速率)或是高速率(二分之一時鐘速率)而進行優(yōu)化;最后將 FPU 連接至 FCB 并將 FPU/FCB 時鐘鏈接至適當?shù)臅r鐘(通常是二分之一或三分之一處理器時鐘速率。)

圖 3——通過 BSB 向?qū)?頂部)以及系統(tǒng)組裝視圖將 FPU 添加至現(xiàn)有 PowerPC 處理器設(shè)計方案中

評論