基于FPGA的數字式光端機的研究與設計

4 并串/串并模塊

本文引用地址:http://www.cqxgywz.com/article/83485.htm低壓差分信號是由ANSI/TIA/EIA-644-1995定義的用于高速數據傳輸的物理層接口標準(LVDS)。它具有超高速(速率可達1.4Gb/s)、超低功耗和低電磁輻射等特性,因而是在銅介質上實現千兆位速率通信的優選方案。而總線形低壓差分信號LVDS是LVDS技術在多點通信領域的擴展,它要求有更大的驅動電流(10mA)和更好的阻抗匹配設計。

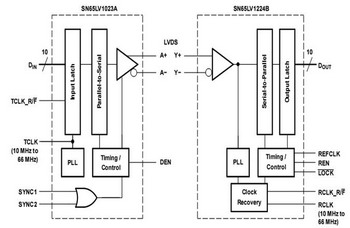

SN65LV1023和SN65LV1224是TI公司推出的10位總線型低壓差分信號的應用芯片組。其中SN65LV1023是可將10位并行CMOS或TTL數據轉換為具有內嵌時鐘的高速串行差分數據流的串化器;而SN65LV1224則是接收該差分數據流并將它們轉換為并行數據的解串器,它同時又可以重建并行時鐘。采用該器件組進行數據串化時采用的是內嵌時鐘,這樣可有效地解決由于時鐘與數據的不嚴格同步而制約高速傳輸的瓶頸問題。此處的硬件電路設計如圖4所示。

圖4 并串轉化硬件示意圖

系統軟件設計

系統軟件主要是對系統控制核心的FPGA的編程。整個程序基于模塊化、結構化的軟件開發思想編寫。所用的開發工具是Altera公司出品的FPGA集成開發環境QuartusII,開發語言采用當今比較流行的大規模集成電路Verilog開發語言。

系統軟件功能實現了A/D控制模塊、語音編碼控制模塊、并串轉換控制模塊、串并轉換控制模塊、D/A控制模塊、語音解碼控制模塊和反向數據的收發控制模塊。

1 A/D控制模塊

A/D控制模塊以FPGA為主控核心,為AD9280提供采樣時鐘;同時采集AD9280A/D轉換后的數字量。

FPGA系統時鐘頻率為32MHz,對于AD9280的采樣時鐘為16MHz,對系統時鐘進行二分頻后提供給AD9280。同時,在分頻后的輸出時鐘的上升沿對A/D轉換的結果進行讀取,讀取的結果存入FPGA中進行下一步應用。程序如下所示。

module PcmControl(clk_in,reset,tdd,tdc,tde,pcm_data);

……

always@(posedge clk_in)

begin

if(reset)

begintdc<=0; end

elsebegin

if(cnt0==7)

begin

tdc<=~tdc;

cnt0<=0;

end

else

cnt0<=cnt0+1;

end

end

always@(posedge tdc)

begin

if(cnt1==140)

begin

tde<=~tde;

cnt1<=0;

end

else

cnt1<=cnt1+1;

end

always@(posedge tdc)

begin

pcm_data<=tdd;

end

endmodule

其中,clk_in是FPGA系統時鐘,reset為系統復位信號。信號tdd是PCM編碼芯片的輸出;信號pcm_data用來存放PCM編碼數據;信號tdc是PCM編碼時鐘信號;信號tde是PCM編碼使能時鐘。

fpga相關文章:fpga是什么

評論