基于SOPC的嵌入式高速串口設計(06-100)

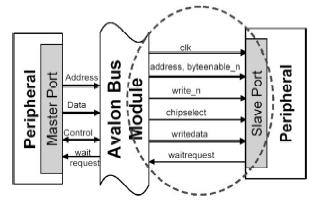

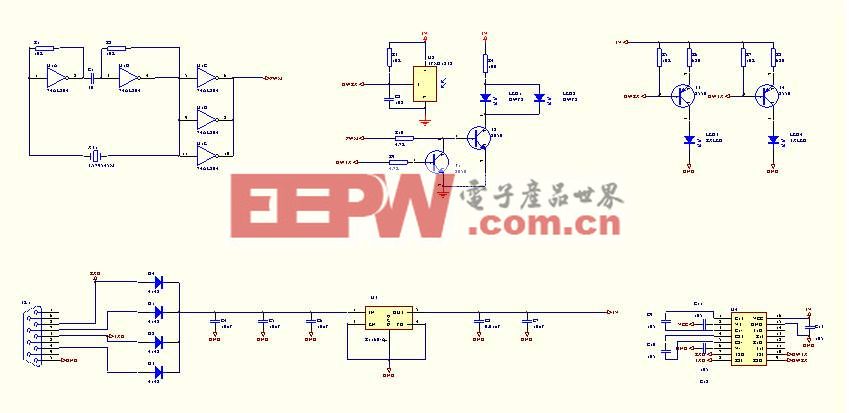

用戶定義的Avalon總線模塊設計

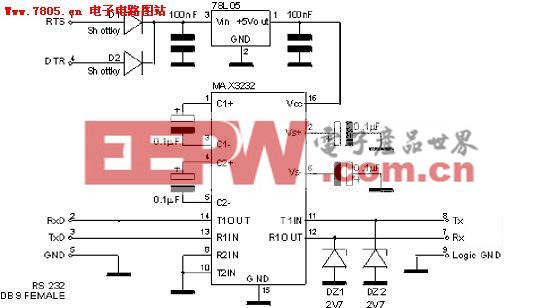

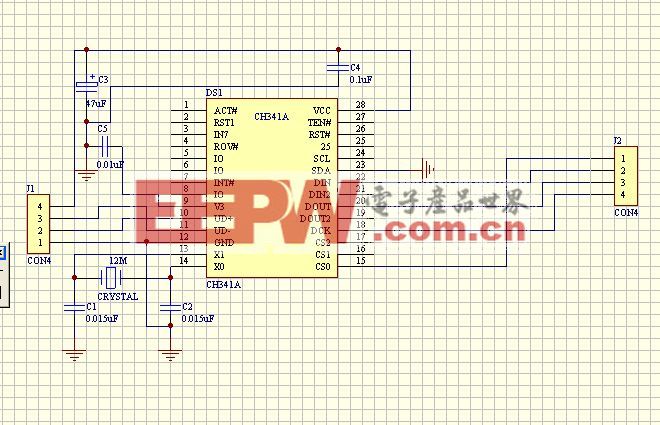

本文引用地址:http://www.cqxgywz.com/article/81083.htm NiosII是基于RISC技術的通用嵌入式處理器芯片軟內核,它特別為可編程邏輯進行了優化設計,也為可編程單芯片系統設計了一套綜合解決方案。Avalon總線是一種高效的總線結構,主要用于連接片內處理器NiosII和各種外設IP core,以構成可編程系統芯片(SOPC)。數據幀發送電路和數據幀接收電路通過Avalon總線和NiosII處理器連接在一起,Avalon總線規范定義了主端口和從端口之間通過Avalon總線模塊傳輸數據所需的信號和時序。設計時通信模塊采用從端口傳輸模式,數據幀發送電路采用具有外設控制等待周期的從端口寫傳輸模式,發送電路除串行數據輸出線外,還必須提供符合Avalon總線傳輸要求的信號線,即Address、Writedata(31..0)、Write_n、Chipselect、Waitrequest,與NiosII工作同步的時鐘信號clk,當CPU要發送數據時,將Address、Write_n信號有效,同時將要發送的32位數據裝載到Writedata(31..0)上,而同步時鐘clk一直處于工作狀態,當clk上升沿判斷到以上信號有效后,Avalon總線對Address譯碼,然后置Chipselect有效,而發送電路VHDL程序設計時必須判斷Address、Chipselect是否有效,如果有效,則在下一個clk上升沿前將Waitrequest置為無效,數據傳送電路就從Avalon總線獲取Writedata數據,如果Waitrequest有效,則這個總線周期就成為等待周期,其他信號以及數據信號保持不變,但外設必須保證不會使Waitrequest無限期地保持有效,這樣會使得一個從外設能夠將Avalon總線永久“掛起”,其連接關系和時序關系如圖4所示。同理,數據接收電路采用具有外設控制等待周期的從端口讀傳輸模式,可以將串轉并后的數據送入到NiosII中進行處理。

軟件設計

基于NiosII的C語言設計,可以采用單線程模式,也可采用uc/基于NiosII的C語言設計,可以采用單線程模式,也可采用uc/OSII多任務操作系統。這里對接收和發送的數據處理主要采用以下指令實現,“IORD(base, 1)”讀指令,其中base就是需要讀取的外設基地址,數據接收電路作為外設在建立SOPC Builder時定義的名稱為“user_uart_rxd”,則base應改為“user_uart_rxd_base”,而第2個參數‘1’表示其偏移地址;“IOWR(base, 1, data)”寫指令,其中base是需寫入外設基地址,數據發送電路作為外設在建立SOPC Builder時定義的名稱為“user_uart_txd”, 則base應改為“user_uart_txd_base”,而第2個參數‘1’表示其偏移地址,第3個參數data是發送數據。

計算機仿真波形如圖5、圖6所示。它們之間的時序關系參照本文的第二部分。

結語

運用此5Mbit/s的UART進行通信,效果十分穩定、可靠性高,傳輸速度快,采用RS485接口模式傳輸距離遠,同時不易被干擾以至出現誤碼、丟數據、丟幀等情況。因此采用SOPC嵌入式系統設計技術可以實現系統設計的小型化、集成化和高可靠性,還可以減少風險、降低成本、縮短開發周期。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論