FPGA基軟件無線電(04-100)

——

FPGA IP核

本文引用地址:http://www.cqxgywz.com/article/80918.htm在普通的FPGA 中,已經增加了來自FPGA供應商和其他第3方核開發商的IP核。這些核提供各種DSP功能。然而,這需要集成到實際的硬件中。把這些核集成到商用現成模塊中需要時間和硬件設計經驗。ICS公司提供的FPGA核是完全測試和集成有高性能數據采集和變換器的商用現成模塊。這些模塊提供智能前端產品,因此,降低了系統設計和集成風險。

寬帶數字下變頻器

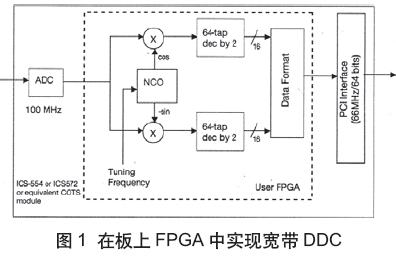

寬帶數字下變頻器(DDC)是任何軟件無線電基系統的主要元件。DDC已基本上改變了通常的無線電設計。DDC能夠簡化RF前端設計,這包括LO和混頻器設計,這是在數字域執行下變頻過程。數字混頻器后面的數字濾波器比傳統模擬濾波器能提供更佳整形濾波。這些濾波器通常是分樣,所以降低了輸出數據率。流行的專用DDC提供可調頻率。然而,它們通常應用目標是窄帶應用。

隨著較寬帶寬需求的增加,系統設計人員正在力圖設計帶寬高達40MHz的寬帶系統。這包括雷達、GPS、遙測裝置、寬帶通信等。對于較寬帶寬,在FPGA中實現DDC需要在FPGA之后有ADC。典型的分樣DDC實現示于圖1。此2分樣DDC提供-0.2*FS~+0.2*FS的最大平頂帶寬(在100MHz ADC取樣)。用100MHz取樣時鐘,這說明40MHz平頂帶寬和每個信道200MBps數據率。DDC提供阻帶抑制超過70dB,為較寬帶寬配置的濾波器可提供2X或4X過取樣因數。

評論