一種基于PCI總線的反射內(nèi)存卡系統(tǒng)設計

![一種基于PCI總線的反射內(nèi)存卡系統(tǒng)設計[圖]](http://editerupload.eepw.com.cn/fetch/20140414/239160_2_0.jpg)

圖5 編解碼控制器結構圖

![一種基于PCI總線的反射內(nèi)存卡系統(tǒng)設計[圖]](http://editerupload.eepw.com.cn/fetch/20140414/239160_2_1.jpg)

圖6 數(shù)據(jù)編解碼仿真時序

3 軟件設計

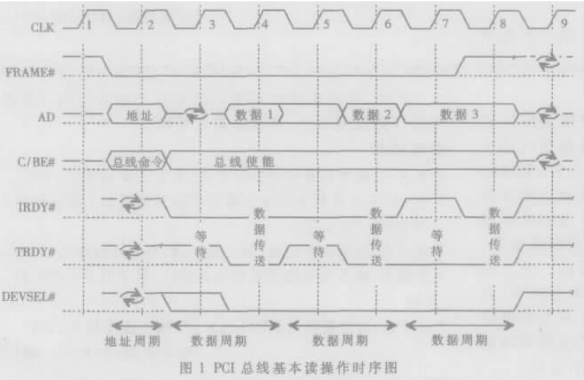

軟件設計包括驅(qū)動程序和應用程序兩部分。驅(qū)動程序提供的API 接口主要包含以下四個方面的功能: 打開和關閉驅(qū)動、配置反射內(nèi)存卡、數(shù)據(jù)傳輸、中斷控制與處理。當應用程序訪問反射內(nèi)存卡資源時,反射內(nèi)存板必須打開, 一個句柄將返回到應用程序。圖7是應用程序處理的流程圖。

![一種基于PCI總線的反射內(nèi)存卡系統(tǒng)設計[圖]](http://editerupload.eepw.com.cn/fetch/20140414/239160_2_2.jpg)

圖7 應用程序流程圖

4 性能測試

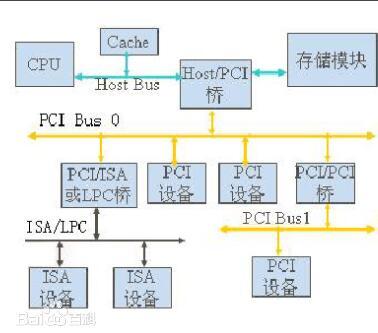

用三塊反射內(nèi)存卡組成環(huán)形反射內(nèi)存網(wǎng), 由節(jié)點1向2 節(jié)點發(fā)送數(shù)據(jù), 節(jié)點2 發(fā)送到節(jié)點3, 由節(jié)點3 向節(jié)點1 發(fā)送確認中斷, 記下此時的終止時間, 如表1 所示。

該反射內(nèi)存卡在windows 操作系統(tǒng)下進行測試,由于windows 為非實時操作系統(tǒng),所以需發(fā)送大批量的數(shù)據(jù)進行速率測試, 以克服操作系統(tǒng)本身的時延。試驗中每次發(fā)送15Mbit 的數(shù)據(jù),根據(jù)傳輸速率= 總數(shù)據(jù)量/ 總時間算出傳輸速率。又由編解碼芯片的串行傳輸速率為1062.5MBd,數(shù)據(jù)傳輸速率為106.25MB/s,而數(shù)據(jù)包的長度是可變的, 從1 個雙字到16 個雙字, 每包數(shù)據(jù)包括32 位的header、32 位的地址數(shù)據(jù)和32 位的校驗和,所以有效的數(shù)據(jù)傳輸速率在26MB/s 至88MB/s,我們測得的數(shù)據(jù)傳輸率為38.9 MB/s 至39.9 MB/s,可以得出該反射內(nèi)存樣卡功能正常。

表1 環(huán)形通訊傳輸速率表

![一種基于PCI總線的反射內(nèi)存卡系統(tǒng)設計[圖]](http://editerupload.eepw.com.cn/fetch/20140414/239160_2_3.jpg)

5 結束語

本文介紹了一種基于PCI 總線的反射內(nèi)存卡的設計方法。給出了硬件電路設計,在FPGA 內(nèi)完成數(shù)據(jù)緩存FIFO 及其控制器、SDRAM 控制器和編解碼控制器的設計, 結構清晰, 集成度高; 介紹了驅(qū)動程序的設計,提供了應用程序接口; 采用三塊反射內(nèi)存卡搭建了驗證系統(tǒng), 實驗證明該反射內(nèi)存樣卡功能正常, 工作穩(wěn)定。

評論