亞微米CMOS電路中VDD-VSSESD保護結構設計二

上述例子中,主要是版圖的設計不當造成在ESD發生時自身結構的損壞。經過分析,對該版圖結構做了一些修改優化。

原因:針對上述理論分析及例子中實際的擊穿點,該結構在1000V即被擊穿的原因主要是N1管的漏區孔距柵的距離d太小所致,d=1.35μm;

目標:改動盡量少的版次達到全面提升該電路的ESD性能的目標;

方案:N1管的L修改為1.2μm,d修改為3μm,改動的版次為多晶版和孔版;

結果:I/O-VDD、I/O/-VSS、I/O-I/O模式下,最低的P95可達到2.50kV,P50、P51、P54、P57、P84可達2.8kV,其余的I/O在3.1kV時仍然通過;在VDD-VSS模式下,當ESD加+3.40kV時,VDD-VSS間短路,所以該模式下抗ESD電壓為3.1kV。

可見,通過修改優化VDD-VSS鉗位結構,其圖2結構自身的抗ESD健壯性大大增強,VDD-VSS的抗ESD能力提高到3kV以上,其余I/O也得到了進一步的提升,使該電路總體ESD性能提高到2.20kV以上,滿足了民品電路的ESD性能要求。要進一步提高該電路的ESD性能,需要對該結構繼續優化,如再增大N1管的漏區孔距柵的距離d及W/L等,其他I/O口的GGNMOS管也需要相應的優化修改,但其總面積可能會相應增加。

4 VDD-VSS兩種電壓鉗位結構的比較

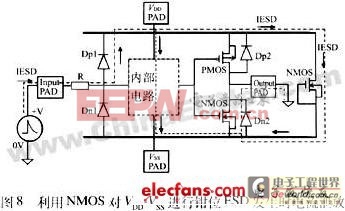

圖8為一種常見的全芯片ESD保護結構的設計,左邊為一個輸入PAD,右邊為一個輸出PAD,最右邊的NMOS管則是常規CMOS工藝電路中最常見的VDD-VSS電壓鉗位結構的設計。其設計要注意管子本身尺寸的邏輯設計,也要注意其版圖的詳細規則設計。它不屬于電壓檢測電路。在電路正常工作時,相當于一個反向二極管;當有ESD發生時,則NMOS管漏區的PN結反向擊穿,寄生的NPN導通從而泄放大電流并使VDD-VSS間的電壓鉗位。

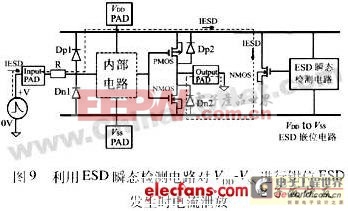

圖9中最右邊的VDD-VSS電壓鉗位結構的設計則為一種ESD瞬態檢測電路,該電路一種詳細的設計方案即為圖2的結構設計。具體作用上面已經進行了詳細的分析闡述。主要是比較一下圖8、圖9兩種VDD-VSS電壓鉗位結構的優劣。

在ESD發生時,兩個結構對VDD-VSS都有電壓鉗位作用,關鍵是各自電流的泄放能力的差異。一般管子的正向導通比反向擊穿能力耐更高的ESD電壓,承受更大、更低阻抗的ESD電流,且ESD電流泄放更均勻。在亞微米CMOS IC中,VDD-VSS直接的GGNMOS大管可能不足以耐較高的ESD電壓,該結構更有利于ESD性能的提升,同時其版圖設計面積也更大。只有在亞微米以下的CMOS電路的設計中,才需要考慮。

評論