基于FPGA的AES算法芯片設計實現

其中Round1-Round3、FinalRound是由組合邏輯完成的操作,都能夠在一個時鐘周期內執行完成。這種風格的代碼在生成流水線電路時,還需要控制指令的配合。

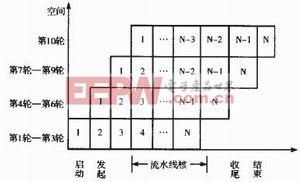

圖3是拆分輪運算的流水線時空圖。圖中數字表示數據分組的序號,整個流水線操作由啟動、發起、流水線核、收尾和結束5部分組成,當進入流水線核時的效率是最高的。

圖3 拆分輪運算的流水線時空圖

用加速比(Speedup)可以衡量采用流水結構之后加密過程相對于非流水結構速度的提高。計算流水線加速比的基本公式為![]() 。

。

設加密N個分組,10輪運算每輪的運算時間為!,則

![]()

當N的取值無限增大時,這個比值將接近于3.33…。因而使用流水結構數據處理速度比非流水結構提高到3倍多。

仿真實驗和結果

圖4為加密過程時序。針對128bit明文分組和128bit初始密鑰的AES算法,在QuartusII軟件下,采用中間相遇的設計方法將頂層模塊化圖形設計與底層VHDL語言描述相結合實現。實驗時選用APEX20KE系列的EP20K1500EFC33-3為目標芯片進行仿真和功能驗證。密鑰裝載完畢之后每加密輸出一個分組需3個時鐘周期,吞吐率為689.500Mbits/s。使用了3056個LUTs,81626個Memorybits,可以滿足SDH標準速率STM-4規定的622.080Mbits/s的要求。

|

圖4 加密過程時序

結合FPGA的結構特點,本設計實現的IP核具有如下特點:接口設計靈活,外部接口的設計和定義可以根據不同加密芯片的接口設計要求現場改動。資源占用小,脫密電路采用與加密電路部分復用的結構實現,從而節省了資源。設計支持重用,在算法實現頂層設計時采用了模塊化設計方法,結構清晰,可以根據不同的功能需求進行改動,利于設計重用

評論