基于CPLD/FPGA的多功能分頻器的設計與實現

采用VHDL語言可以實現計數器的下降沿觸發翻轉,并且CPLD/FPGA具有可并行執行的特性,可以保證兩種不同的觸發翻轉以及分頻時鐘輸出保持同步,所以上述分頻方法可以基于CPLD/FPGA予以實現。

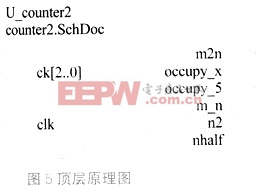

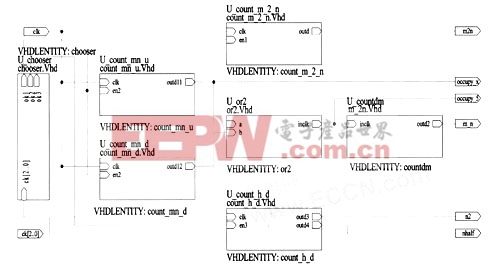

本設計使用第三方EDA開發工具Protel DXP。該開發工具支持層次原理圖及VHDL語言混合設計并能進行編譯、時序和功能仿真,支持Xilinx、Altera、Lattice等公司的系列 CPLD/FPGA器件,并且具有設計直觀、層次性好等優點。在設計中采用兩級原理圖和底層VHDL語言三級結構來實現,使整個的設計以功能模塊化,便于程序修改、功能升級和分頻系數的設定。對于分頻值的設定采取了軟件設定的方法,即只需在VHDL語言程序中按照自己的需求對相應的參數作修改、設定,而且設定值的取值靈活。頂層原理圖、次級原理圖分別如圖5、6。

本次設計CK延時3ns后設值為111,即功能模塊全部選中工作;偶數倍分頻模塊中模N計數器N設置為2,實現四分頻;奇數倍分頻模塊中模2N+1計數器 N設置為1實現三分頻,占空比X設置為1即分頻系數為1/3,模M計數器M值設置為2實現2M*(2N+1)=12分頻;N-0.5倍分頻模塊中N設置為 3,實現2.5分頻。從方針波形中可以看出,實現了通用多功能分頻器。若要得到其他值,只需修改相應功能模塊的VHDL語言中的相關的參數,再進行編譯、綜合適配、下載即可。

分頻器相關文章:分頻器原理

評論