基于CPLD的數據采集與顯示接口電路仿真設計

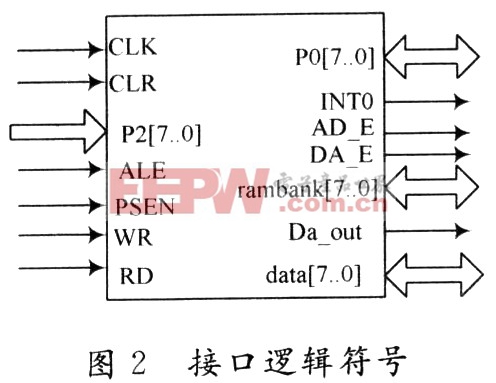

系統工作過程如下:ALE為地址鎖存使能信號,當下降沿來時,將P0口將低8位地址送入可編程芯片CPLD/FPGA中的地址鎖存器,然后在P2口和P0口形成的16位地址及WR信號共同作用下,將P0口的數據送入可編程芯片。單片機通過兩條指令MOVXDPTR@ ADDR和MOVX @DPTR A將數據寫入芯片。在P2口和P0口形成的16位地址及RD信號共同作用下,將AD0809轉換后數據data送入單片機的P0口。單片機通過兩條指令 MOVX DPTR @ADDR和MOVXA@ DPTR將數據讀入P0口。設置A/D轉換器件片選信號ad_e和DA轉換器件片選信號da_e,設置數據輸入/輸出口data[7..0]。單片機與FPGA通信接口程序(名為MCS51)通過編譯后,生成的邏輯符號如圖2所示。本文引用地址:http://www.cqxgywz.com/article/191769.htm

CPLD使用EPM7128時鐘為16 MHz有源晶振,首先使用CLK對復位信號采樣,8051的復位信號要求是高電平維持2個機器周期,2個機器周期就是2×12=24個振蕩周期,對復位信號連續采樣10次,若是一直為高電平,就產生片內復位使能信號。其他片內寄存器以這個復位信號做同步復位,對WR.RD,ALE都做了采樣,避免毛刺干擾。

1.3 AD0809與CPLD/FPGA狀態機接口設計

1.3.1 AD0809狀態機功能設計

狀態機的最簡結構一般由兩個進程構成,即主控時序進程和主控組合進程。一個進程描述時序邏輯輸出,另一個進程描述組合邏輯包括進程問狀態值的傳遞邏輯以及狀態轉換值的輸出。將AD0809與CPLD/FPGA的接口設計系統劃分為兩部分,即數據單元和控制單元。數據單元包括保存運算數據和運算結果的數據寄存器,也包括完成數據運算的組合邏輯電路。控制單元用來產生信號序列,以決定何時進行何種數據運算,控制單元要從數據單元得到條件信號,以決定繼續進行那些數據運算。數據單元要產生輸出信號、數據運算狀態等有用信號。數據單元和控制單元中,有兩個非常重要的信號,即復位信號和時鐘信號。復位信號保證了系統初始狀態的確定性,時鐘信號則是時序系統工作的必要條件。狀態機通常在復位信號到來的時候恢復到初始狀態,每個時鐘到來的時候內部狀態發生變化。從AD0809的初始狀態開始,也就是狀態機復位以后開始的狀態。在建立每個狀態時都寫出關于這個狀態的文字功能描述,AD0809狀態機功能描述與相應引腳的取值如下:

1. 3.2 ADC0809狀態機程序設計

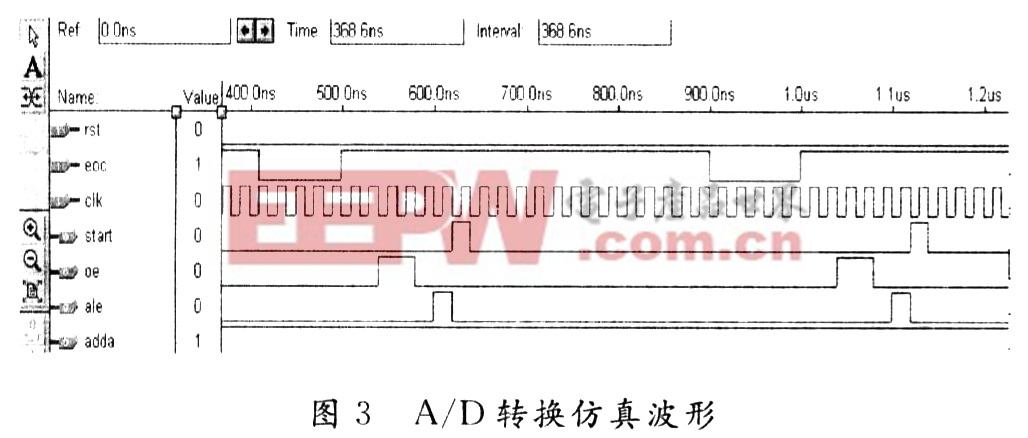

ADC0809為單極性輸入,8位轉換精度逐次逼進式A/D轉換器。其采樣速度為每次轉換約100μs。在轉換開始前由地址鎖存允許信號ALE將3位地址鎖入鎖存器中以確定轉換信號通道。EOC為轉換結束狀態信號,由低電平轉為高電平時指示轉換結束,此時可讀人轉換好的8位數據。EOC在低電平時指示正在進行轉換。START為轉換啟動信號,上升沿啟動。OE為數據輸出允許高電平有效。CLK為ADC轉換時鐘輸入端口500 kHz左右。為了達到A/D器件的最高轉換速度,A/D轉換控制器必須包含監測EOC信號的邏輯,一旦EOC從低電平變為高電平即可將OE置為高電平,然后傳送或顯示已轉換好的數據[DO..D7]。狀態機由三個進程組成ADC,AD_STATE和DATA_LOCK。ADC是此狀態機的主控組合邏輯進程,確定狀態的轉換方式和反饋控制信號的輸出工作過程中首先監測系統復位信號RST,當其為高電平時使此進程復位至初始態ST0。啟動A/D轉換信號START在狀態ST3搜索轉換狀態信號EOC由0變1時即在狀態ST4開啟輸出。使能信號OE在下一狀態使LOCK產生一個上跳沿從而在此時啟動進程DATA_LOCK將由0809轉換好的8位數據鎖進鎖存器ADC_DATA。根據時序電路圖通過狀態機設計程序完成與CPLD/FPGA芯片的連接。圖3為狀態機程序仿真結果。

1.4 BCD碼轉換與顯示電路設計

當ADC0809的基準電壓(Vref)為5.12V時,最小電壓準位是5.12/28=O.2V。分析模擬輸入電壓與輸出電壓的對應關系可知,當ADC0809的D[7..0]收到的數據信號為10000110(即86H)時,則高4位1000為2.56V,而低4位0110為O.12V,所以最后的電壓輸出結果是2.68V。為了方便后續的電壓數據顯示,在此將輸出電壓表示成12位的BCD碼形式。將高4位數據D(7..4)轉換為對應的高12位BCD碼H(11..0);將低4位數據D(3..0)轉換為對應的低12位BCD碼L(11..O)。在程序中首先用VHDL語言描述一個新的進程Process(regl),然后采用case…when …語句,生成并行結構的電路。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論