基于FPGA和PCI的高精度測速板卡的設計與實現

1.2 改進的M/T測速算法

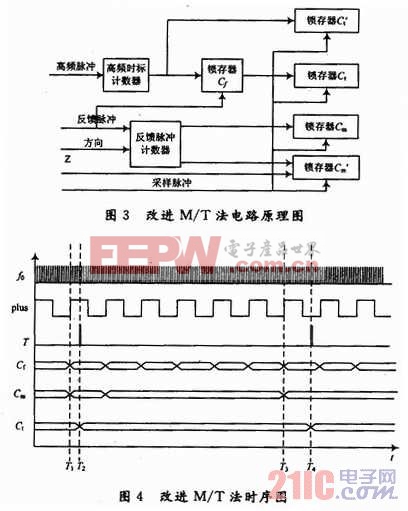

圖3展示了改進M/T法的電路原理,這是實現高精度的硬件基礎。圖4為改進M/T法的時序圖。本文引用地址:http://www.cqxgywz.com/article/191386.htm

對圖3及其時序圖4的分析可以看出:本測速電路在每個反饋脈沖時鎖存高頻時鐘的計數值,兩個采樣周期間的高頻時標增量值Ct實際表示為T2前一個反饋脈沖上升沿到T4前一個反饋脈沖上升沿的高頻時標增量,而在采樣周期內每個反饋脈沖到來都對反饋脈沖計數器計數,兩個采樣脈沖采得反饋脈沖增量值Cm實際表示為T1~T3之間的反饋脈沖增量值,位置的反饋脈沖增量值則是在Cm的基礎上考慮方向得到的,那么結合32位浮點運算,這種測速方法就解決了采樣時機不確定的缺點。

根據上述分析,通過差分處理就可得到當前實際采樣間隔內的反饋脈沖增量值Cm和高頻時標增量值Ct:![]()

這樣得到的速度是當前實際采樣間隔內的平均速度:![]()

式中:KR為反饋信號脈沖當量;fo為高頻時標頻率。

在實際采樣點T2處,高頻時標信號fo的邊沿不能總與反饋脈沖信號plus的邊沿保持一致,因而會產生±1個高頻時標當量的計數誤差,從而影響這種測速算法的測速精度。因此高精度數字測速算法的測速相對誤差為:![]()

動態位置算法不僅關注已經發生的反饋脈沖數量,也關注反饋脈沖的發生時刻,其硬件基礎是依據圖3所示邏輯電路的。根據當前有效采樣周期的定周期采樣點和實際采樣點之間的時間差:![]()

并根據改進的M/T法得到被測對象的平均速度vn,由vn和△Tn相乘就可以計算出時間差△T(n)中所包含的動態位置信息,因此由當前有效采樣周期內的增量式高精度動態位置信息可以得出位置量:![]()

可根據這種方法完成測位置的功能。

評論