基于SOPC的雷達多功能接口模塊的設計與實現

2.4 TVJ子模塊視頻控制電路設計

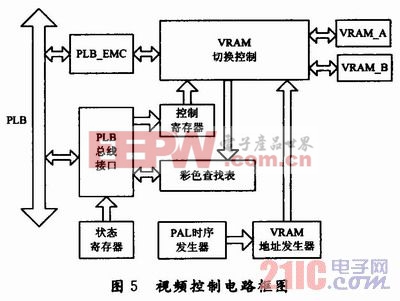

視頻控制電路是TVJ子模塊的關鍵電路,它包括PLB總線接口、VRAM切換控制電路、視頻時序發生器、VRAM地址發生器、彩色查找表和控制/狀態寄存器,如圖5所示。本文引用地址:http://www.cqxgywz.com/article/191090.htm

PLB總線接口主要完成視頻控制電路與系統PLB總線的符合IBM CoreConnect總線規范的無縫接口電路。VRAM切換控制電路完成系統對兩塊顯存讀/寫控制的交替切換。PLB_EMC是Xilinx嵌入式開發套件EDK自帶的PLB總線外部存儲器控制接口IP。VRAM_A和VRAM_B都是存儲視頻圖像數據的顯存,切換控制電路在任意時刻總是將1塊顯存掛接在PLB_EMC接口上,而從另一塊顯存讀出視頻圖像數據經過調色板變換后輸出給D /A產生要顯示的彩色圖像信號。修改顯示畫面時CPU通過PLB總線先對掛接在PLB_EMC接口上的VRAM_A進行改寫,同時用VRAM_B讀出的數據來完成顯示,然后通過設置控制寄存器切換到另一狀態,再用VRAM_A完成顯示,而對VRAM_B改寫以使兩塊顯存數據保持相同,這樣系統讀/寫顯存時就不會影響顯示了,同時VRAM切換控制電路可以設置為只對高8位、只對低8位和對16位這3種顯存存取方式,以此來實現顯存的快速存取和背景疊加顯示功能。

PAL視頻時序發生器產生顯示所需的時鐘、行場同步和消隱信號,提供給VRAM地址發生器子模塊,用于形成尋址外部顯存的地址。將FPGA內部的存儲器資源例化為一個128 K×4 b的ROM,然后將1幀時間長度(40 ms)的信號設計成.coe格式文件作為ROM的初始化數據。

VRAM地址發生器就是根據PAL視頻時序發生器給出的行、場同步和消隱信號來產生讀顯存需要的地址,并與PAL制式信號時序同步。

彩色查找表的功能是將從顯存讀出的視頻圖像數據經過查表處理后形成24位RGB彩色數字視頻提供給D/A變換輸出到顯示器顯示。查找表共512個單元,將其分為兩部分,0~255為第一個表,256~511為第二個表,顯存輸出的數字視頻要么通過第一個表,要么通過第二個表來轉換,不能同時,當數字視頻高8位為全0時,將使用低8位去索引第一張表,當高8位不為全0時,將使用高8位去索引第二張表,這樣系統可以由軟件來靈活地設置修改彩色查找表的內容從而實現多種分層和疊加的彩色顯示方式。

3 SoPC技術在設計中的應用

開發采用Xilinx公司的EDK(嵌入式開發套件)和ISE工具軟件。EDK工具包中集成了硬件平臺生成器(Platgen)、軟件平臺生成器(Libgen)、仿真模型生成器(Simgen)、軟件編譯器(Mb-gcc/ppc-gcc)和軟件調試工具(Mb-gdb/ppc-gdb)等,通過集成開發環境XPS,用戶可以調用上述所有工具,來完成嵌入式系統開發的整個流程。

可配置嵌入式系統的配置層面包括,處理器配置:如指令或數據緩沖配置,協處理器或硬件加速器;系統配置:如I/O外設選擇、定制、DMA選擇、存儲器外設選擇、定制等;用戶專用外設和電路:將專用電路設計成為用戶自定義的IP Core,然后在系統中添加調用來實現。用戶自定義的IP Core要求必須用HDL設計并滿足片內總線接口和EDK工程的規范,如有專門目錄結構和處理器外設定義文件(.MPD)、外設分析定義文件(.PAO)等。如果自定義的IP Core要具有軟件驅動,那設計還要完全符合相應的總線底層驅動接口規范。總之將SoPC技術應用在接口模塊的設計中具有以下優點:由于接口模塊往往是實現專用功能的嵌入式計算機小系統,在芯片RAM資源可以滿足系統的設計要求的前提下,可以將系統存儲器都集成到FPGA內部,大大減小體積和功耗,減少芯片數量;硬件設計的更改可通過重新配置FPGA器件來實現,增加設計靈活性,降低設計風險。

4 結語

由于FPGA內部集成的通信接口和IP Core的種類的不斷豐富,使得在更多的應用領域使用SoPC技術進行嵌入式系統設計已成為可能。該多功能接口模塊已成功地應用于實際產品中,取代了以往3個單獨的接口模塊,大大減小了體積,降低了功耗,在提高了性能的同時也提高了系統的可靠性,并為設計體積更小、性能更強的雷達接口模塊提供了發展方向。

評論