基于NoisⅡ的程控數字信號源設計

1.2 AD9854信號產生單元

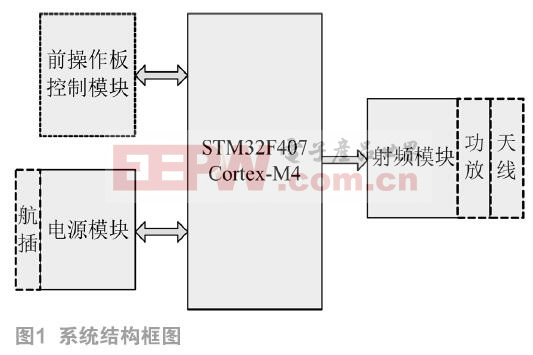

AD9854的DDS核具有48位的頻率分辨率。輸出的信號頻率最高達150 MHz、頻率分辨率可達1μHz。將AD9854的8位數據線、5位地址線以及一些控制信號線(復位、寄存器數據更新引腳、FSK引腳等)引出連接到FPGA的通用I/O口上,使得FPGA可以完成對AD9854的相關配置與控制。AD9854的時鐘輸入采用了差分時鐘輸入形式。

1.3 人機交互界面

本單元由液晶顯示單元和PS/2鍵盤輸入單元組成。液晶單元采用ILI9320片上系統(SoC)驅動器。有18位數據線,采用了16 b總線寬度的i80-systemMPU接口,PWM為液晶背光亮度調節引腳;RS為寄存器選擇信號,低電平選擇索引或狀態寄存器,高電平選擇控制寄存器;

2 系統軟件設計

NoisⅡ軟核CPU是整個系統的控制部分,集成在FPGA內部,由SoPC Builder定制。將需要的IP組合在一起,設定各組件的地址和中斷優先級,各IP Core通過Avalon總線邏輯互連,自由配置處理器的CACHE大小、指令集ROM大小、片內RAM和ROM大小、I/O引腳數目和類型、中斷引腳數目、定時器數目、通用串口數目、擴展地址和數據引腳等處理器的性能指標。NoisⅡ集成開發環境提供了創建C/C++應用工程的向導、管理和編譯工程功能、運行和調試程序功能和最終程序的FLASH的燒寫。編程采用C語言。

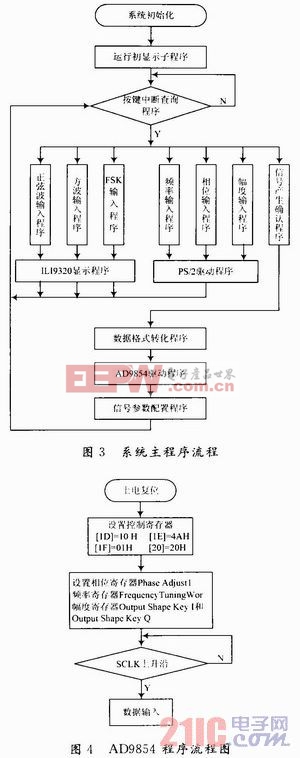

系統首先進行初始值,然后顯示開機系統界面,軟核CPU接收到鍵盤中斷輸入的顯示信號和向AD9854輸出指令后,啟動顯示和輸出程序模塊,使AD9854產生響應的信號輸出。對設置數據進行存儲防止設置信息掉電丟失。整體程序設計流程如圖3所示。

2.1 AD9854驅動程序

(1)AD9854主要負責各種波形信號的產生,采用并行模式,其程序框圖如圖4所示。本文引用地址:http://www.cqxgywz.com/article/190480.htm

評論