基于FPGA的電梯控制器系統設計方案

2.2 模塊設計與實現

對于分頻器模塊、按鍵請求模塊、電梯控制器模塊和指示模塊和顯示模塊這四個模塊,電梯控制器模塊和指示模塊涉及到電梯各種運行情況的處理,其算法是最復雜的,也是最容易出錯的。本文采用使用有限狀態機來設計該模塊,具體的算法描述如下。

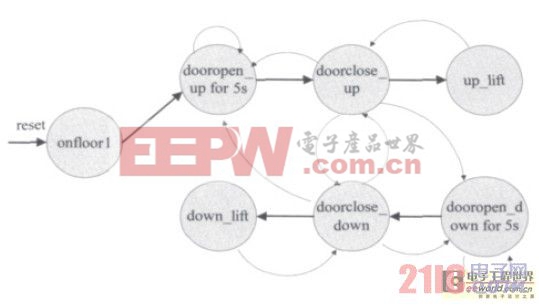

將電梯運行定義為7個狀態,具體的狀態定義如下:

S0:onfloor1,表示在樓層1;

S1:dooropen_up,上升過程中,電梯開門5s;

S2:doorclose_up,上升過程中,電梯關門;

S3:up_lift,表示電梯上升一層;

S4:dooropen_down,下降過程中,電梯開門5s;

S5:doorclose_down,下降過程中,電梯關門;

S6:down_lift,表示電梯下降一層。

各狀態在滿足一定的條件下轉換,具體狀態轉換如圖2所示。

圖2 電梯控制器狀態轉換圖

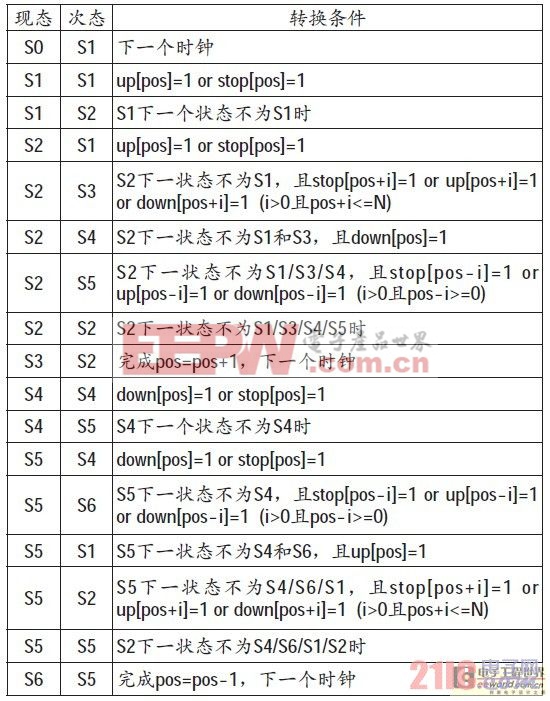

表1 電梯控制器狀態轉換條件

上表中, pos 表示當前樓層, up[pos ] 、down[pos]、stop[pos]分別表示當前樓層的向上、向下、和停止銨鈕的狀態。

顯然,上述算法并未對樓層數作限制,也就是說該算法適合于任意樓層的電梯控制器。

2.3 仿真驗證

本文根據上述算法,采用Verilog HDL語言在FPGA上實現了一個三層電梯控制器。對于實現來說,三層電梯或者多層電梯的控制器只是Verilog代碼數量的不同,其算法則完全是本文提出的算法,沒有區別。本文只所以實現了一個三層電梯控制器,是因為硬件開發環境的資源(包括按鈕的數量、指示燈的數量)僅滿足三層電梯控制器的驗證。

評論