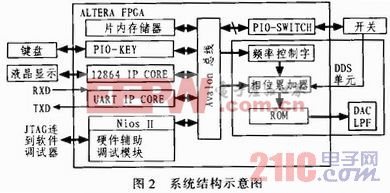

基于FPGA的DDS基本信號發生器的設計

3 各模塊設計

3.1 波形數據存儲方式

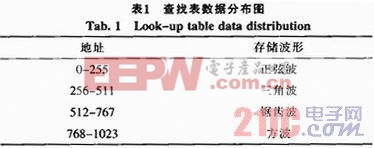

通過對DDS基本原理的分析得知只需更換波形存儲器中的波形采樣數據,就可以得到所需波形的信號。波形數據存儲方式包括順序存儲方式和間隔存儲方式,本設計采用順序存儲方式將方波,三角波,正弦波,鋸齒波4種波形采樣數據全部依次存儲在一個查找表里,數據分布情況如表1所示。通過改變尋址首地址,并在該波形數據存儲地址范圍內循環尋址,從而實現對所需信號波形的輸出。具體實現方法在累加控制模塊中有介紹。

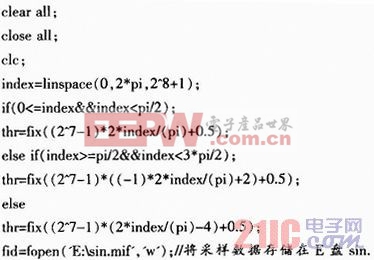

DDS模塊中的波形數據存儲器是用QuartusⅡ中的MegaWizard Plug_In Manager工具添加的LPM_ROM IP核,此存儲器ROM是用波形存儲文件.mif進行初始化,波形數據可以用matlab等工具生成,用matlab生成4種波形的波表數據程序如下:

評論