Hummingbird加密算法的硬件架構(gòu)設(shè)計

1.3 塊加密過程

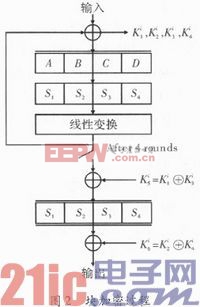

Hummingbird加密算法采用4個相同的塊加密模塊,每個塊加密過程均是16 bit,密鑰為64 bit。其過程如圖2所示。塊加密過程中的S—Box如下表所示。當(dāng)中的線性變換過程定義如下

L(m)=m⊕(m×6)⊕(m×10) (1)本文引用地址:http://www.cqxgywz.com/article/189549.htm

2 算法的FPGA硬件架構(gòu)實現(xiàn)

由于Hummingbird加密算法是一種輕型加密算法,主要針對硬件資源受限的平臺和應(yīng)用場合,因此,提出了一種硬件資源使用較少的FPGA架構(gòu)。

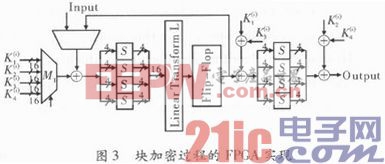

首先,對于塊加密過程,用4個時鐘周期來完成4輪的塊加密,由于每輪加密過程的密鑰均不同,因此需要一個選擇器來選擇正確的密鑰,塊加密過程的FPGA架構(gòu)如圖3所示。

評論