基于SoPC的FIR濾波器設計與實現

2 FIR濾波器的實現

Altera提供的FIR Complier是結合Altera FPGA器件的FIR Filter Core,DSP Builder與FIR Compiler可以緊密結合起來。DSP Builder提供了FIR Core的應用環境和仿真驗證環境。

2.1 建立模型文件

為了調用FIR IP Core,在Simulink環境中新建模型文件,放置Sigtlal Compiler模塊和FIR模塊。啟動Simulink的方法:打開Matlab,在主命令窗口直接鍵入Simulink,按回車即可。然后打開Altera DSP Builder模塊,在MegaCore Functions調出fir_compiler_v7_0。

2.2 配置FIR濾波器核

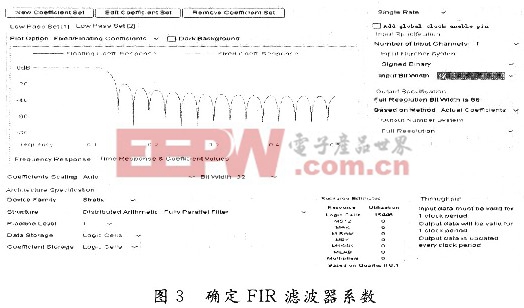

雙擊模型中的FIR模塊,在彈出來的選擇窗口中有:關于這個核(about this core)、程序說明書(documentation)、顯示元件(display symb01)、步驟1確定參數(Stepl:Parameterize)和步驟2生成(Step2:Generate)等4個不同的選項。點擊stepl,便打開了FIR濾波器核的參數設置窗口,如圖3所示。本文引用地址:http://www.cqxgywz.com/article/187846.htm

由圖3可見,濾波器的系數精度為32位,器件為CycloneⅢ,結構為并行濾波器,結構選擇了1級流水線,濾波器由LC邏輯宏單元構成,系數數據存于FPGA的M9K模塊中,1個輸入通道,32位有符號并行輸入,全精度數據輸出。設定后會直接顯示濾波器的頻率響應(frequency res-ponse)或時域響應及系數值(timeresponse coefficeient values)。由其頻率響應圖可以看出,此FIR濾波器為低通濾波器。如果不符合設計要求,則可以通過對Edit Coefficient Set選項,對濾波器進行重新配置。

2.3 生成VHDL語言

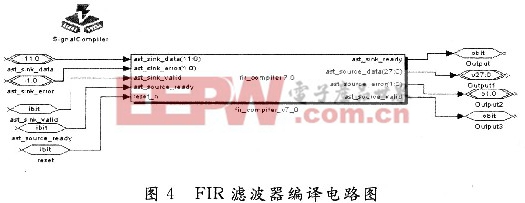

完成FIR濾波器核配置后,便可得到設計好的濾波器,加入輸入/輸出信號,形成如圖4所示電路。點擊SignalCompiler,再選擇Anal-yze,選擇Sigle step compilation中的Convert MDL to VHDL,就可以生成對應的VHDL語言。

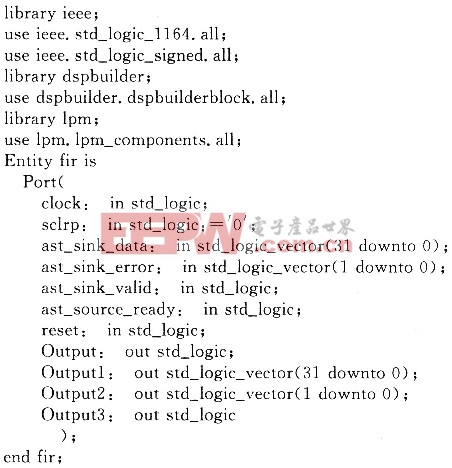

在QuartusⅡ中打開編譯后生成的fir.qpf工程文件,可以得到濾波器的VHDL語言,其部分代碼如下:

編譯成功后,可以將其轉換成元件。

評論