基于MCU和FPGA的LED圖文顯示屏控制系統

3.4 譯碼器

譯碼器模塊主要是產生16路的分區(qū)信號(低電平有效)分別控制16個鎖存器,把16個分區(qū)的顯示數據分別鎖存在相應的鎖存器中。

3.5 數據鎖存器組及移位寄存器組模塊

數據鎖存器組模塊由16個8位鎖存器組成鎖存器組,鎖存16個分區(qū)的數據。移位寄存器組模塊由16個8位移位寄存器組成,把各路鎖存器中8位并行數據轉換成同時輸出的16路串行數據,驅動LED顯示屏,實現數據的并串轉換。

其生成的元件符號如圖6所示。其中,DATA_IN[7.0]為每個分區(qū)的8位并行數據輸入,SCLK為移位時鐘,CLR為清零信號,LOAD為數據鎖存信號,CS[150]為16分區(qū)的輸入信號(接譯碼器的輸出),DATA_OUT[150]為16路的串行數據輸出。

3.6 脈沖發(fā)生器

系統采用1/16的掃描方式,把數據分為16分區(qū),16分區(qū)數據同時傳送。假設刷新的頻率為60Hz(即周期為16.67ms),每一行顯示的時間約為16.67ms/16=1.04ms。每行有1024位,則移位脈沖周期為1.04/1024=102s,即移位頻率為0.983MHz以上才能滿足要求。

由于移位脈沖是數據讀取模塊時鐘的2分頻,因此系統的時鐘至少1.97MHz以上,本系統采用50MHz時鐘源。

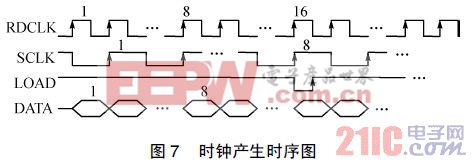

其時序圖如圖7所示。

其中,RDCLK為FPGA讀取數據時鐘;SCLK是串行輸出的移位時鐘,是RDCLK的2分頻;LOAD是數據鎖存信號,每次讀完16個分區(qū)中的某個字節(jié)數據DATA后產生鎖存信號,數據鎖存在數據鎖存器組中,其時鐘是RDCLK的16分頻。

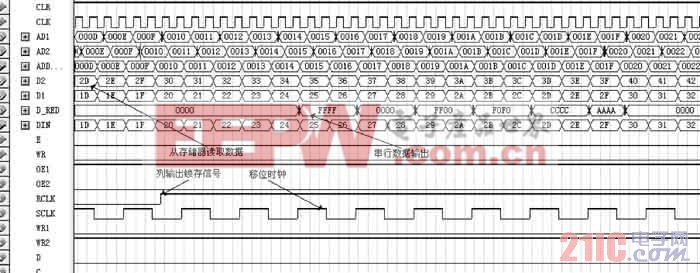

4 FPGA控制模塊的仿真測試

在QuartusII5.1中建立一個工程,并建立原理圖文件,把單片機與FPGA接口及數據讀寫模塊、讀地址發(fā)生器、譯碼器、行地址發(fā)生器、數據鎖存器、移位寄存器、脈沖發(fā)生器等單元模塊所生的模塊元件符號連接起來,構成總控制模塊邏輯圖并對其功能仿真。仿真結果如圖8所示,從存儲器中讀取16字節(jié)數據,經并串轉換輸出16路的串行數據。從波形圖分析,功能正確,且各輸出端口信號均符合時序要求。

5 結語

FPGA是在線可編程芯片,可以根據不同的用戶要求進行不同的編程,縮短了系統的開發(fā)周期并節(jié)約了硬件的開發(fā)成本。本文以FPGA為主芯片,較完整地設計了大屏幕LED單色圖文顯示屏控制系統。隨著LED顯示屏技術的發(fā)展,FPGA與ARM或DSP等芯片的組合,必將在雙色顯示屏和彩色顯示屏領域獲得廣泛的應用。

評論