如何利用FPGA降低手持設備MPU的功耗

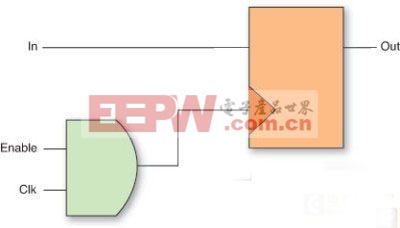

設計人員可以禁用傳送到這部分電路的時鐘來達到這個目的。一種簡單的做法是將時鐘信號與使能信號相“與(AND)”,如圖2所示。如果使能信號是低電平,那么與門的輸出將保持低電平。如果使能信號為高電平,與門將輸出時鐘信號。

本文引用地址:http://www.cqxgywz.com/article/165671.htm

圖2:一種簡單的時鐘選通機制

還可以使用其它方法。如果可能并且拓撲又支持的話,可以通過復接地址和數據線來減少信號線數量。在我們這個例子中,到視頻編碼器的輸出是16位數據,我們可以把它復接成8位,然后分別在時鐘的兩個沿(上升沿和下降沿)發送出去。這樣做也能節省動態功耗。此外,選擇串行接口代替并行接口也能降低功耗。使用帶較低電容負載的LVTTL或LVCMOS I/O也很有用。

嵌入式處理器

將處理器嵌入到FPGA中是手持設備設計人員可以采用的又一種策略,它可以帶來很多好處。首先,減少了定制處理器帶來的上述挑戰。其次,外設和處理器之間的交互發生在FPGA內部,因而可以減少I/O數量。由于I/O會消耗相當多的功率,此舉也能達到一定程度的節能效果。賽靈思的Virtex-5版本支持PowerPC 440處理器、硬處理器和MicroBlaze軟處理器,所有這些處理器都可以被設計人員用來創建高端或低端應用系統。

隨著90m和65nm半導體技術的發明,門的尺寸在不斷縮小,導致靜態功耗問題越來越突出,在對功耗指標越來越敏感的今天,這是一個極具挑戰性的現象。由于功耗問題獲得了眾多FPGA供應商的重視,在這個領域中已出現許多令人興奮的新技術。低功耗設計將決定一個系統的集成能力有多強,業界也迫切需要將注重功耗的設計技術標準化。

評論